3,430,095

J. J. BIALIK ET AL CATHODE RAY TUBE BEAM POSITIONING SYSTEM EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet

Filed July 8, 1965

3,430,095

J. J. BIALIK ETAL

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Sheet <u>2</u> of 44

Feb. 25, 1969 3,430,095 J. J. BIALIK ET AL CATHODE RAY TUBE BEAM POSITIONING SYSTEM EMPLOYING COMPOSITE SIGNALS Filed July 8, 1965 Sheet \_ TK6 READ HEAD AMP OUTPUT Ī 4|w , W3(A) W3(A) 1, W4 (E) 4|4 4|-€|4 æ. 14  $m \mid m$ 2 2 2  $\begin{vmatrix} ACC & ENT & T1 \\ \frac{2}{3} & \frac{2}{4} & \frac{3}{1} \end{vmatrix}$ 72 2 2 WI(TI) TRACK MOTION DRUM ACC ENT -m 12 DEAD TIME W3(A) Ī. ACC ENT 55 4 3

Ŧ2,

(II) IM

J. J. BIALIK ET AL 3,430,095

CATHODE RAY TUBE BEAM POSITIONING SYSTEM EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet <u>4</u> of 44

| FLIP FLOP | FF. | FF* | FF® OUT |

|-----------|-----|-----|---------|

| I         | OV  | -6V | "I"     |

| ш         | OV  | -6V | "1"     |

| ш         | ov  | -67 | 618     |

## FIG\_B

FIG\_9

J. J. BIALIK ET AL 3,430,095

CATHODE RAY TUBE BEAM POSITIONING SYSTEM EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet \_\_\_\_\_5 of 44

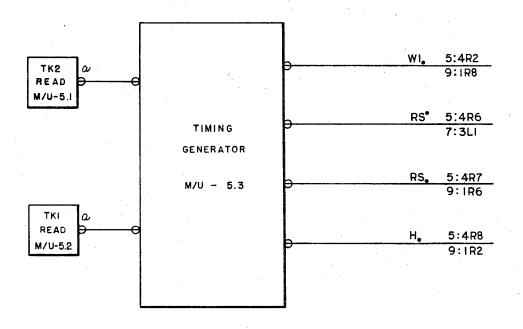

(5:4)FIG\_10

3,430,095

J. J. BIALIK ETAL

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet <u>6</u> of 44

3,430,095

J. J. BIALIK ETAL

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet \_\_\_\_\_\_\_ of 44

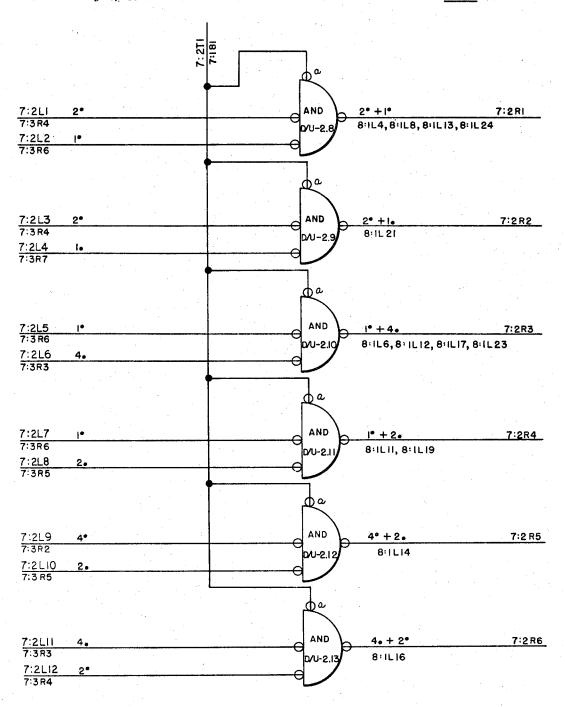

FIG\_12 (7:2)

3,430,095 J. J. BIALIK ET AL

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet 8 of 44

3,430,095

J. J. BIALIK ET AL

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet 9 of 44

J. J. BIALIK ET AL

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet \_\_/O of 44

FIG\_15 (9:1)

J. J. BIALIK ET AL 3,430,095

CATHODE RAY TUBE BEAM POSITIONING SYSTEM EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet \_\_//\_ of 44.

J. J. BIALIK ET AL

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet 12 of 44

J. J. BIALIK ETAL

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet <u>/3</u> of 44

| FLIP FLOP | "o"  | u <sub>l</sub> u . | F.F. OUT |

|-----------|------|--------------------|----------|

| 工         | GND. | 6V                 | Q        |

| П         | GND. | -6V                | Q        |

| III       | GND. | -12V               | Q        |

∼ GND,= POS. VOLTAGE LEVEL

~-6VOLTS OR -12VOLTS = NEG. VOLTAGE LEVEL

FIG\_18

FIG.LS

J. J. BIALIK ET AL

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet \_\_\_\_\_\_\_ of 44

FIG

FIG\_2L

Filed July 8, 1965

FIG\_ 23

J. J. BIALIK ET AL 3,430,095

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet \_ /6 of 44

FIG\_24

J. J. BIALIK ET AL

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet \_\_/7 of 44

J. J. BIALIK ET AL

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

EIG

J. J. BIALIK ET AL 3,430,095

CATHODE RAY TUBE BEAM POSITIONING SYSTEM EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet \_\_/9 of 44

FIG\_30

FIG. 31

FIG\_32

FIG\_33

J. J. BIALIK ET AL 3,430,095

CATHODE RAY TUBE BEAM POSITIONING SYSTEM EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet \_20 of 44

## FIG\_

FIG...35

J. J. BIALIK ET AL 3,430,095

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet 21 of 44

FIG.

J. J. BIALIK ET AL CATHODE RAY TUBE BEAM POSITIONING SYSTEM EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet \_22 of 44

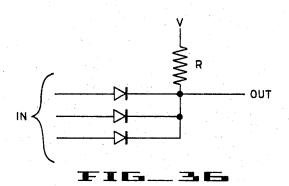

FIG. 36

FIG.

J. J. BIALIK ET AL CATHODE RAY TUBE BEAM POSITIONING SYSTEM EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet <u>23</u> of 44

## FI6\_40

FIG\_41

3,430,095 J. J. BIALIK ET AL CATHODE RAY TUBE BEAM POSITIONING SYSTEM EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet <u>25</u> of 44

3,430,095 J. J. BIALIK ET AL CATHODE RAY TUBE BEAM POSITIONING SYSTEM EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet <u>26</u> of 44

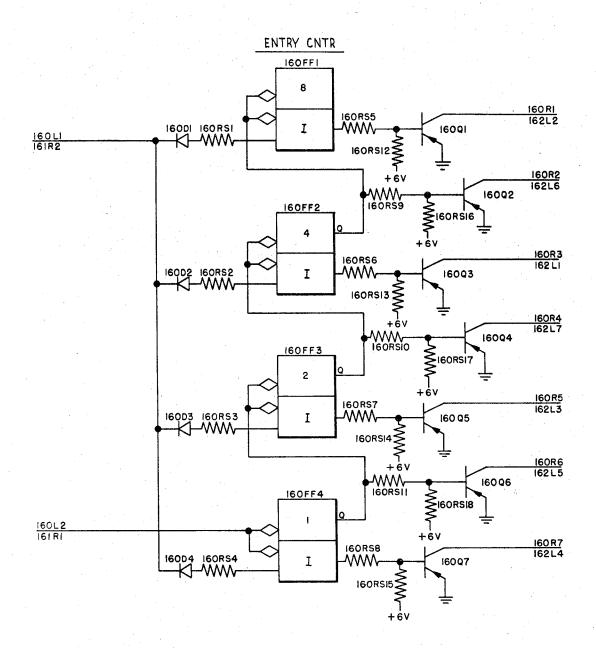

FIG\_45 (160)

3,430,095

J. J. BIALIK ETAL

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet <u>27</u> of 44

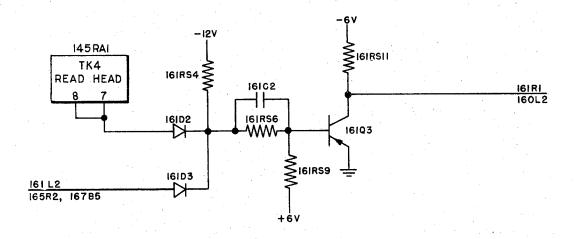

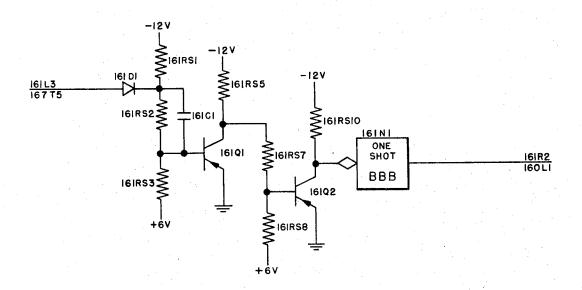

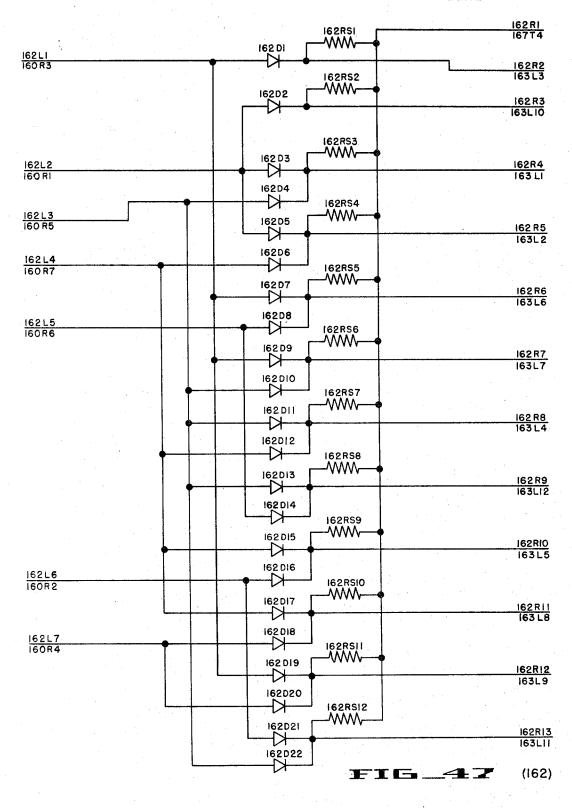

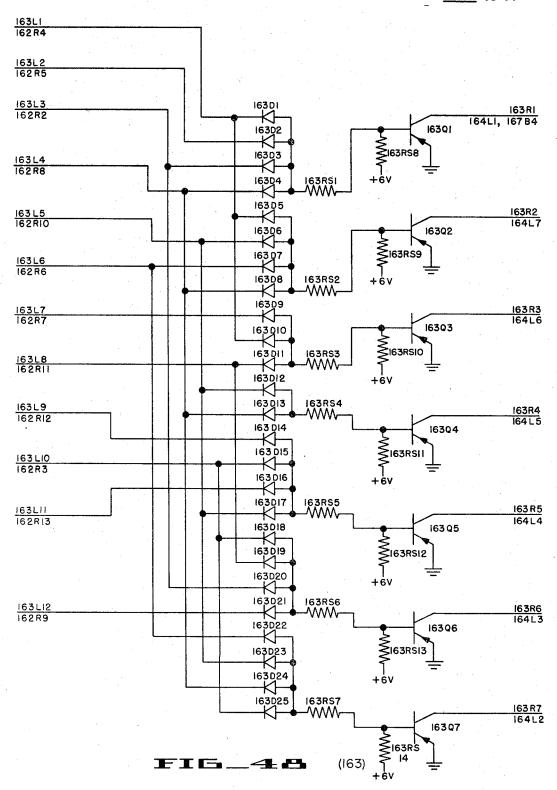

(161)

3,430,095

J. J. BIALIK ET AL CATHODE RAY TUBE BEAM POSITIONING SYSTEM EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet <u>28</u> of 44

3,430,095

J. J. BIALIK ETAL

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet <u>29</u> of 44

3,430,095

J. J. BIALIK ETAL

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet 30 of 44

J. J. BIALIK ETAL

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Sheet <u>3/</u> of 44

Filed July 8, 1965

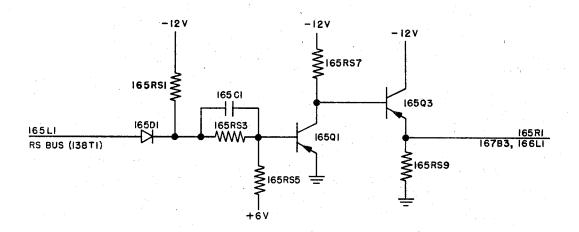

FIG... (165)

J. J. BIALIK ET AL CATHODE RAY TUBE BEAM POSITIONING SYSTEM EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet 32 of 44

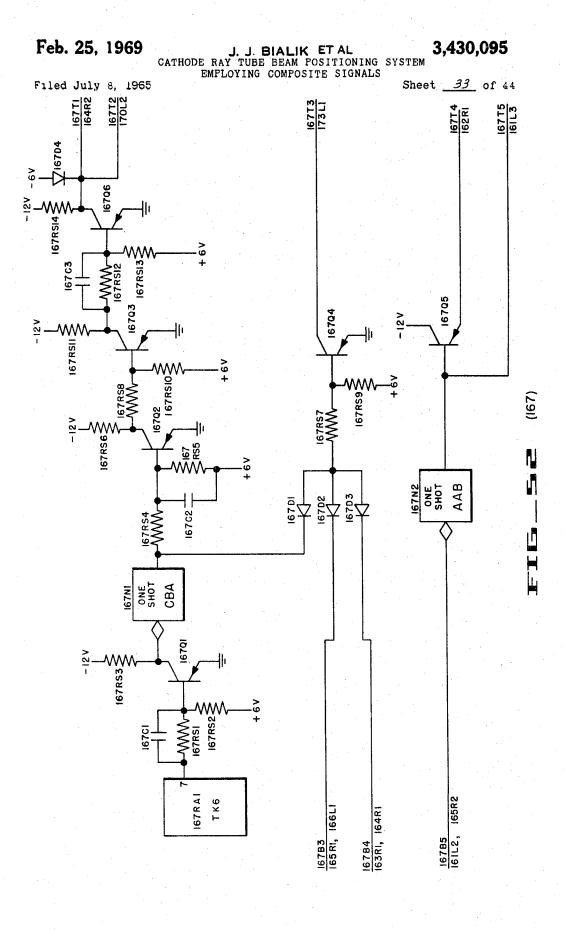

3,430,095

J. J. BIALIK ET AL CATHODE RAY TUBE BEAM POSITIONING SYSTEM EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

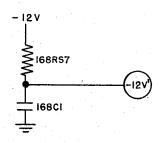

Sheet <u>34</u> of 44

(168)FIG.

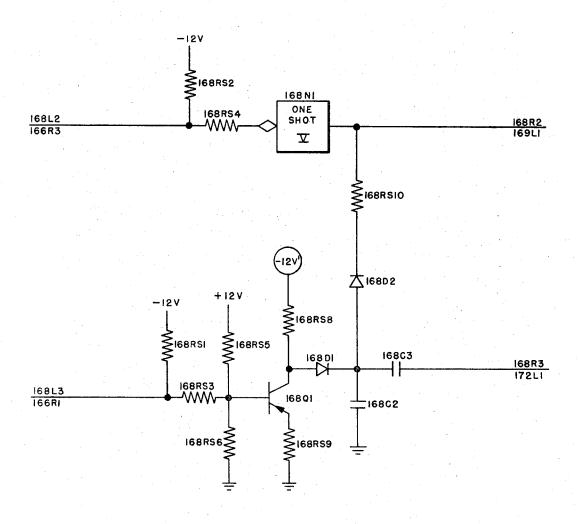

J. J. BIALIK ET AL 3,430,095

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet <u>35</u> of 44

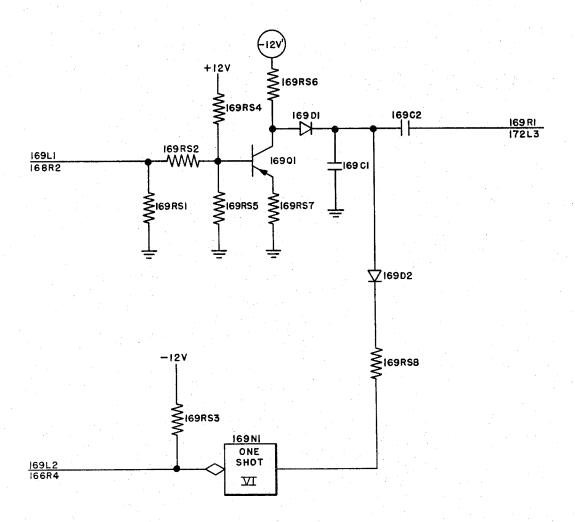

FIG (169) J. J. BIALIK ETAL 3,430,095

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet <u>36</u> of 44

Feb. 25, 1969

3,430,095

J. J. BIALIK ET AL CATHODE RAY TUBE BEAM POSITIONING SYSTEM EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet <u>37</u> of 44

J. J. BIALIK ETAL 3,430,095

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet <u>38</u> of 44

Feb. 25, 1969

3,430,095

J. J. BIALIK ET AL CATHODE RAY TUBE BEAM POSITIONING SYSTEM EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet <u>39</u> of 44

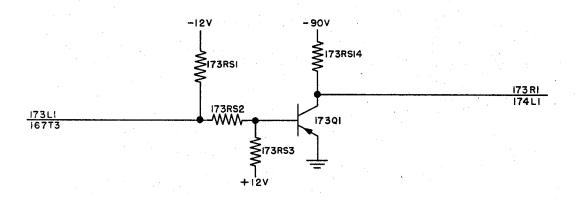

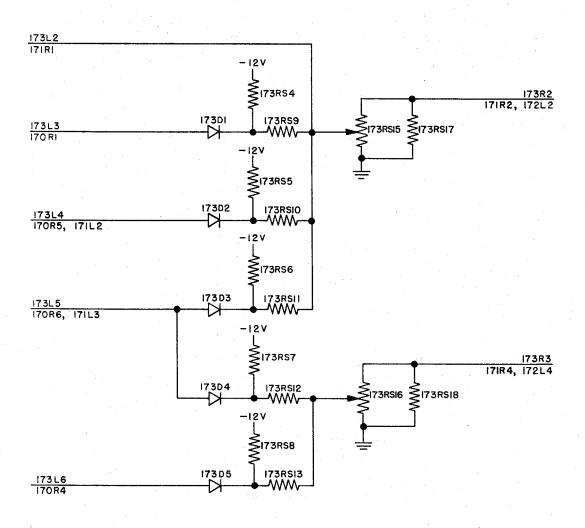

58 FIG. (173)

Feb. 25, 1969

3,430,095

J. J. BIALIK ET AL CATHODE RAY TUBE BEAM POSITIONING SYSTEM EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet 40 of 44

J. J. BIALIK ETAL 3,430,095

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet 41 of 44

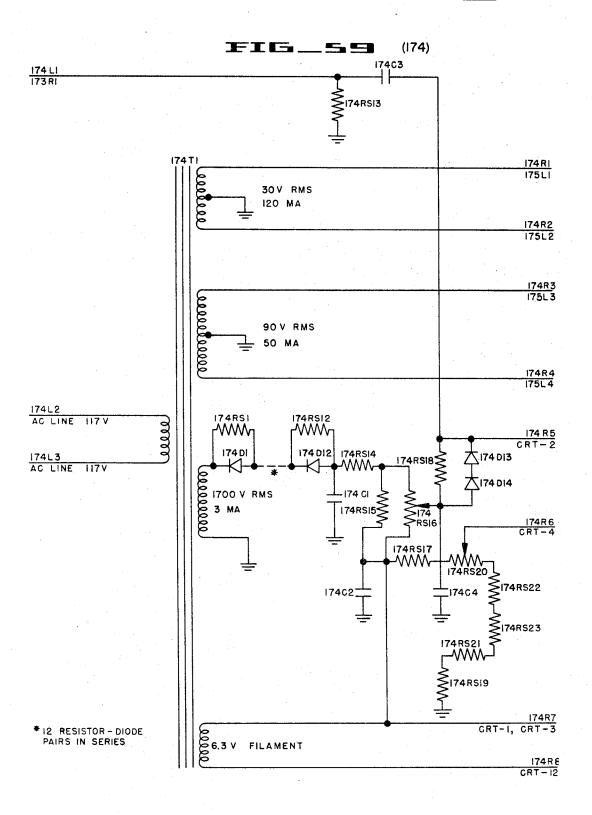

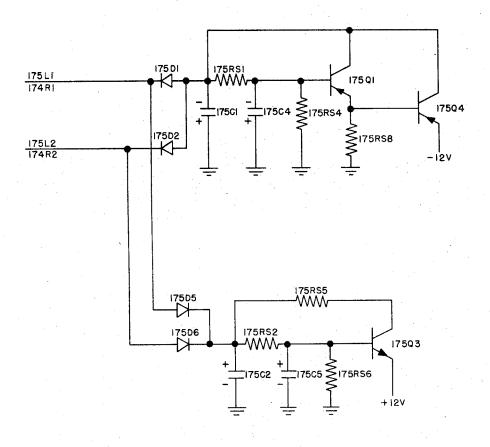

F16\_60 (175)

3,430,095

Filed July 8, 1965

Sheet 42 of 44

Feb. 25, 1969

3,430,095

J. J. BIALIK ET AL CATHODE RAY TUBE BEAM POSITIONING SYSTEM EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet 43 of 44

Feb. 25, 1969

3,430,095

J. J. BIALIK ET AL

CATHODE RAY TUBE BEAM POSITIONING SYSTEM

EMPLOYING COMPOSITE SIGNALS

Filed July 8, 1965

Sheet 44 of 44

# TYPICAL CHARACTER RASTER

#### FIG\_64

#### FIG\_65

3,430,095 Patented Feb. 25, 1969

1

3,430,095 CATHODE RAY TUBE BEAM POSITIONING SYS-TEM EMPLOYING COMPOSITE SIGNALS

Jack J. Bialik, Saint Germain-en-Laye, France, and Dale P. Masher, Menlo Park, and William W. Stevens, Palo 5 Alto, Calif., assignors to Friden, Inc., San Leandro, Calif., a corporation of Delaware

Filed July 8, 1965, Ser. No. 470,370 U.S. Cl. 315—18 Int. Cl. H01j 29/72

# ABSTRACT OF THE DISCLOSURE

There is disclosed an apparatus for and method of controlling the position of a cathode ray tube beam used in character display systems. The beam position is controlled by producing both horizontal and vertical deflection signals, each deflection signal being produced by mixing a beam position signal and a stroke position signal. Provision is made for adding an oscillatory signal to each stroke position signal and for inhibiting the oscillatory signal in response to the condition of a bistable device.

This invention relates to improved character display signal generator apparatus and to improved methods for generating character display signals. Character display generators are well known in the prior art, being described in United States Patent No. 2,762,862 to Bliss, in United States Patent No. 2,766,444 to Sheftelman, in United States Patent No. 2,875,951 to Schreiner, in United States Patent No. 3,090,041 to Dell, and in United States Patent No. 2,834,831 to Giffard. A character display signal generator, then, may be defined as a device capable of producing a plurality of synchronized electrical signals which, when applied to the proper input terminals of a cathode ray tube, an oscilloscope, or the like, cause one or more symbols to be displaced thereupon; said symbols and their configuration, e.g., in rows and columns, being  $_{40}$ selectable by input signals, keyboard actuation, or the like. More particularly, the present invention relates to character display signal generating apparatus and methods which are free from the necessity of employing the costly, specialized and critical components and subcircuits which 45 characterize the devices of the prior art.

As can be seen from the afore-mentioned United States patents, many of the devices of the prior art were characterized by the employment of specialized, costly and critical components and circuitry.

The device of the Bliss patent, for instance, employs a flying-spot cathode ray tube scanner, or a kinescope, within the signal generator itself, in addition to the cathode ray tube employed to display the symbols resulting from the generated signals.

Giffard employs a tube of the class known as monoscopes, or phasmajectors, and also a Williams-type storage tube, both within the signal generator, in addition to the cathode ray display tube.

The device of Sheftelman is also characterized by the employment of costly, specialized and critical components, viz., a plurality of closely-matched delay lines, each having a plurality of critically located taps.

It will be clear from the above, then, that one of the principal problems in the character display signal generating apparatus of the prior art is the high cost, complexity and criticality of certain components and circuits found therein. As is well known to those skilled in the art, these characteristic features of the devices of the prior art render them applicable only to highly specialized applications, wherein cost, compactness and ease of maintenance are not primary considerations. It is to the

2

solution of the problem of providing a novel character display signal generating apparatus and method characterized by low cost, compactness and ease of maintenance that the present invention is directed.

It is therefore an object of the present invention to provide character display signal generating apparatus and methods which are substantially free from the need for special components that characterize present character display signal generators.

It is another object of the instant invention to provide character display signal generators employing noncritical circuitry throughout.

It is a further object of the instant invention to provide methods of generating character display signals, which methods may be carried out without the use of critical apparatus.

It is yet another object of the instant invention to provide a method of generating predetermined symbols upon the faces of fugitive pattern tracing display devices, which method may be practiced without the employment of critical circuits or components, or circuits or components specially adapted only to the practice of that method.

It is still another object of the instant invention to provide apparatus and methods for generating character display signals of minimum band width, thereby ensuring that said apparatus will be characterized by minimum criticality, and maximum ease of maintenance.

It is a yet further object of this invention to provide a deflection system responsive to a binary counter type segment generator system.

It is a yet further object of this invention to provide a voltage weighting circuit responsive to the count of a segment generator for providing proper input voltages to vertical and horizontal amplifiers of a display.

It is a still further object of this invention to provide an oscillator controlled varying signal to the inputs of vertical and horizontal amplifiers for providing line stroke segments defining characters to be displayed on a cathode ray tube.

It is a yet further object of this invention to provide a pair of input signals to a deflection amplifier of a CRT display system composed of a first predetermined weighted voltage and a second varying voltage, the combination thereof providing a line scan at a predetermined position on a cathode ray display tube.

It is a yet further object of this invention to provide a deflection system responsive to a binary device for forming a vertical or horizontal stroke depending upon the condition of said binary device.

It is a yet further object of this invention to provide a pair of input signals to a deflection amplifier, one such input signal being a varying voltage and the second being a ramp function for providing a deflection signal.

Other objects of the instant invention will in part be obvious, and will in part appear hereinafter.

The instant invention, accordingly, comprises the several steps and the relation of one or more of such steps to each of the others, and the apparatus embodying features of construction, combinations of elements, and arrangements of parts which are adapted to effect such steps, all of which are exemplified in the following detailed disclosure. The scope of the instant invention will be indicated in the claims.

For a fuller understanding of the nature and objects of the invention, reference should be had to the following detailed description, taken in conjunction with the accompanying drawings, in which:

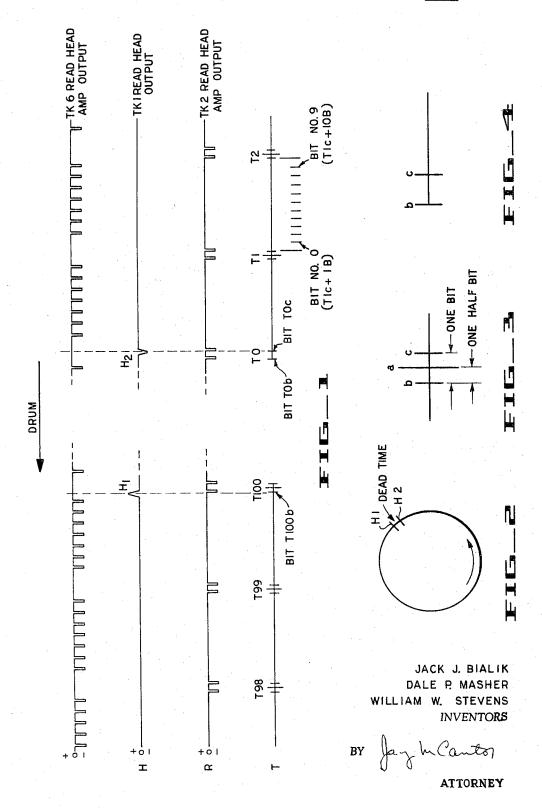

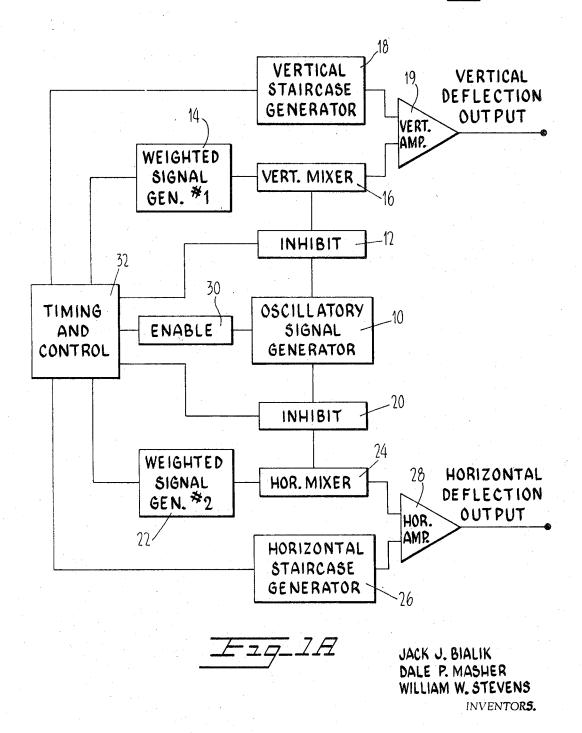

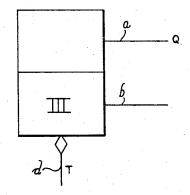

FIGURE 1A is a block diagram of the display device according to the invention.

FIGURE 1 is a pictorial description of the output signals from track 1, track 2 and track 6 read head circuits

of the magnetic drum including a reference scale designated T.

FIGURE 2 is a pictorial description of track 1 of the magnetic drum.

FIGURES 3 and 4 are pictorial explanations of the definition of the signal time periods.

FIGURE 5 is a pictorial description of the registers of track 4 of the magnetic drum and the relationship of the read head therefore.

FIGURE 6 is a description of the timing signals obtained from the timing circuits and the levels of these timing signals during the various time periods of opera-

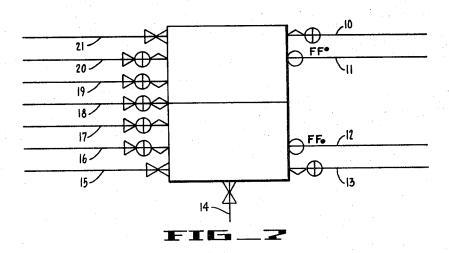

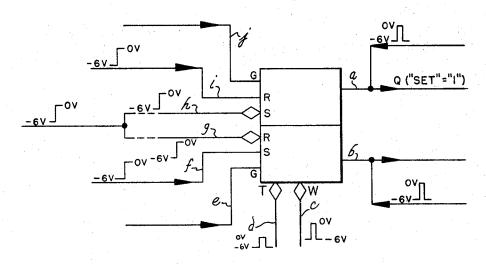

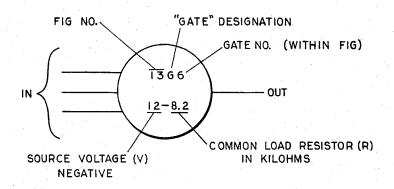

FIGURE 7 is a symbolic diagram of a flip flop as used in the logic diagrams of FIGURES 10 to 17.

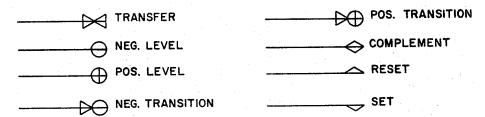

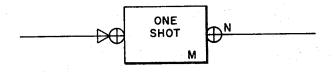

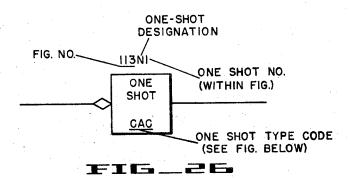

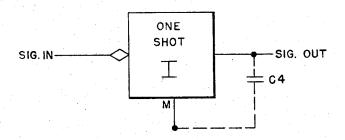

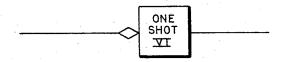

FIGURE 8 is a description of symbols utilized in the description of the logic diagram of FIGURES 10 to 17. FIGURE 9 is a symbolic diagram of a one shot as used

in the logic diagrams of FIGURES 10 to 17.

FIGURES 10 to 17 comprise a logic diagram of the 20 display device in accordance with the present invention. FIGURE 18 is a symbolic diagram of a flip flop as used in the circuit diagram of FIGURES 42 to 60.

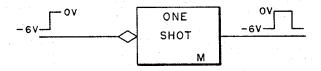

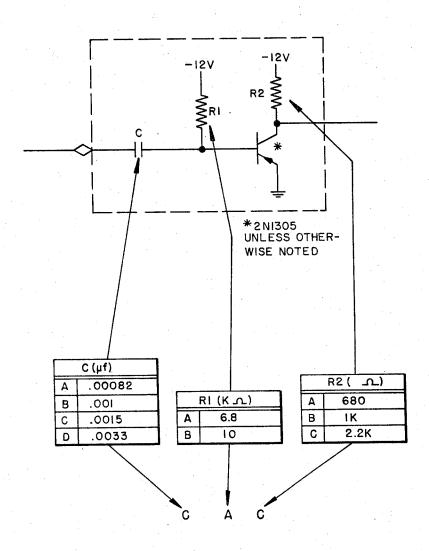

FIGURE 19 is a symbolic diagram of a one shot as used in the circuit diagram of FIGURES 42 to 60.

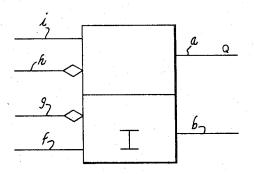

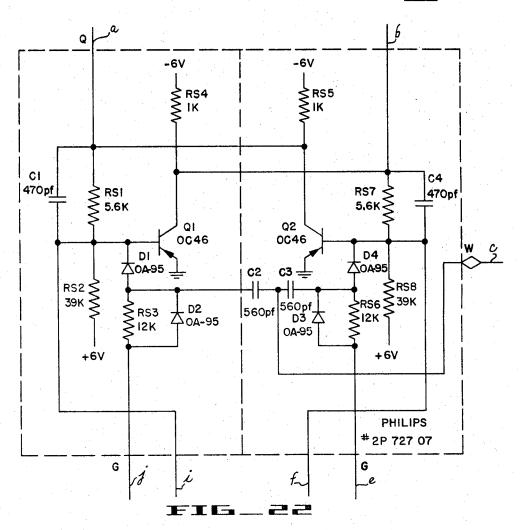

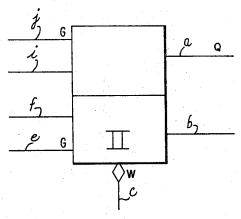

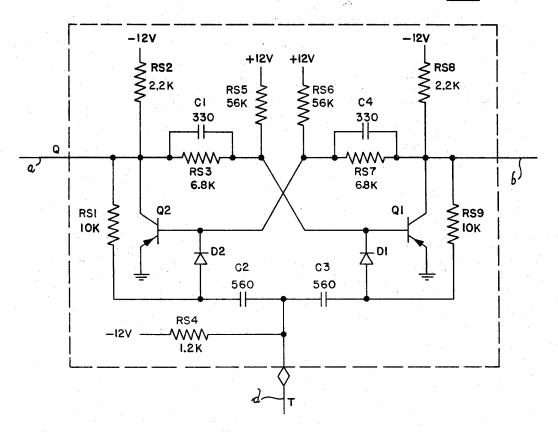

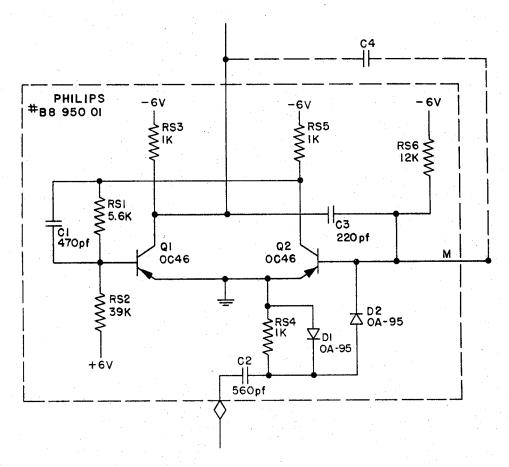

FIGURE 20 is a circuit diagram of a type I flip flop. FIGURE 21 is a symbolic diagram of a type I flip flop. FIGURE 22 is a circuit diagram of a type II flip flop. FIGURE 23 is a symbolic diagram of a type II flip flop. FIGURE 24 is a circuit diagram of a type III flip flop. 30 FIGURE 25 is a symbolic diagram of a type III flip

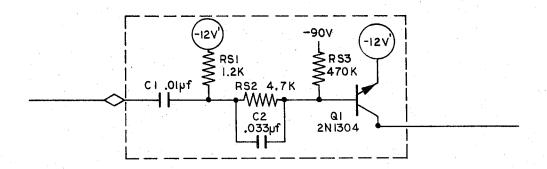

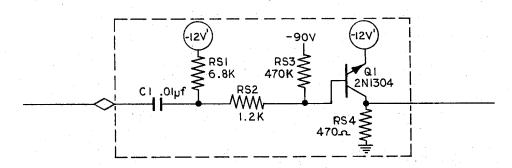

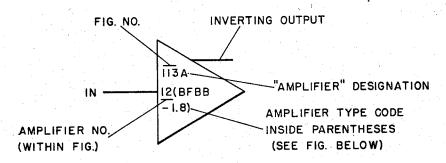

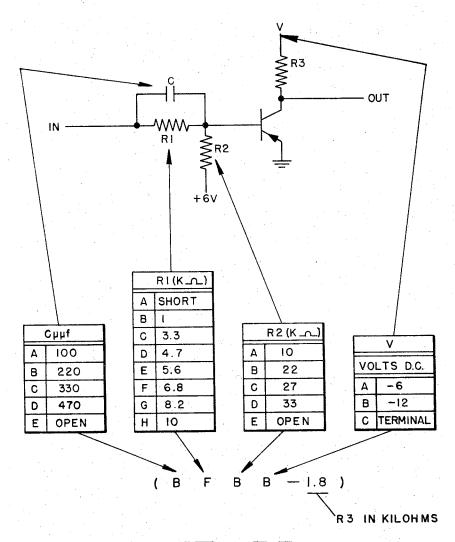

FIGURES 26 and 27 describe the circuit of certain one shots used in the circuit diagram of FIGURES 42 to 60. FIGURE 28 is a circuit diagram of a type I one shot. 35

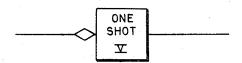

FIGURE 29 is a symbolic diagram of a type I one shot. FIGURE 30 is a circuit diagram of a type V one shot. FIGURE 31 is a symbolic diagram of a type V one

FIGURE 32 is a circuit diagram of a type VI one shot. 40 FIGURE 33 is a symbolic diagram of a type VI one

FIGURES 34 and 35 describe the circuit of the inverters used in the circuit diagram of FIGURES 42 to 60. FIGURES 36 and 37 describe the circuit of certain gating circuits used in the circuit diagram of FIGURES 45 42 to 60.

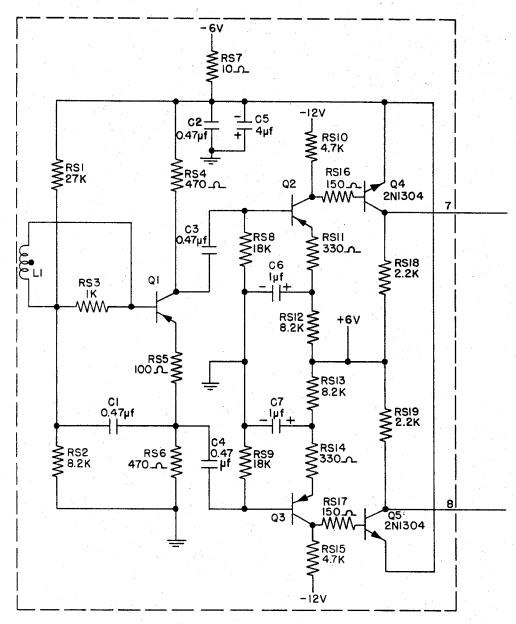

FIGURE 38 is a circuit diagram of the read head circuit used in the circuit diagram of FIGURES 42 to 60. FIGURE 39 is a symbolic diagram of the read head circuit of FIGURE 38.

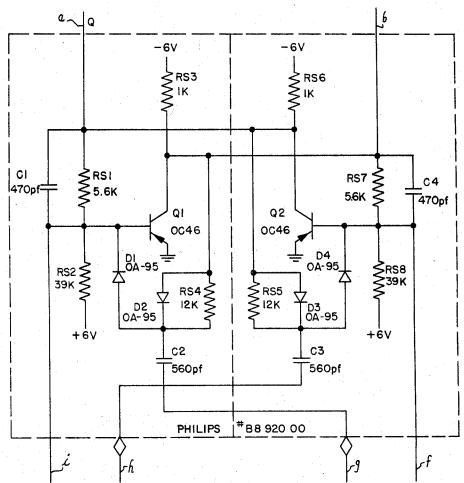

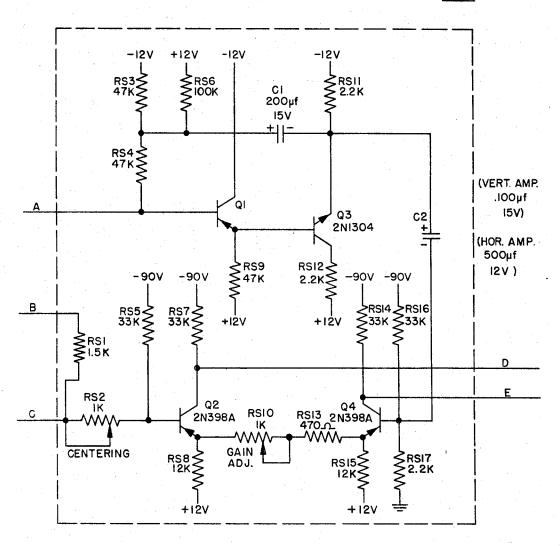

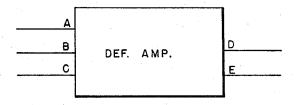

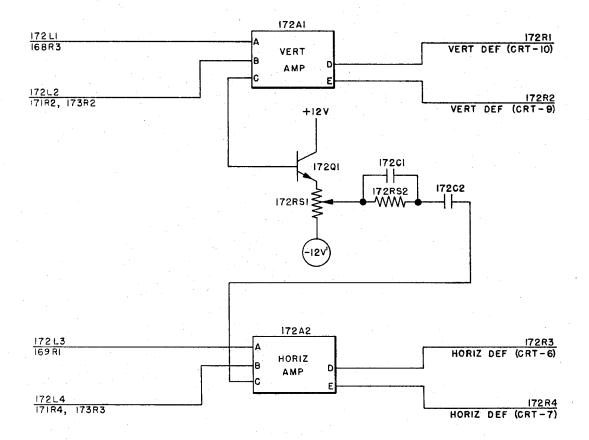

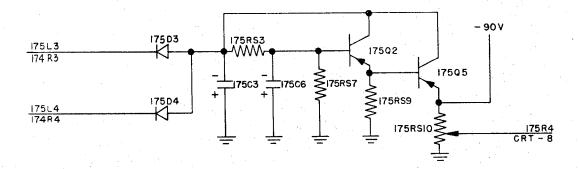

FIGURE 40 is a circuit diagram of the vertical and horizontal deflection amplifiers used in the circuit diagram of FIGURES 42 to 60.

FIGURE 41 is a symbolic diagram of the vertical and horizontal deflection amplifiers of FIGURE 40.

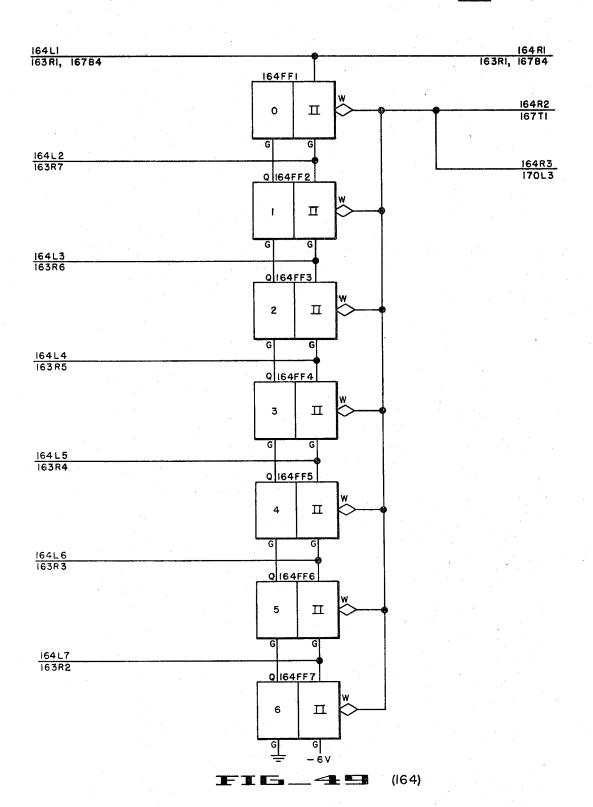

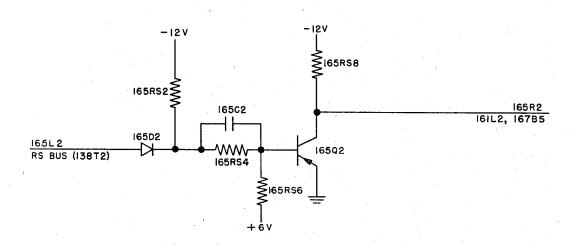

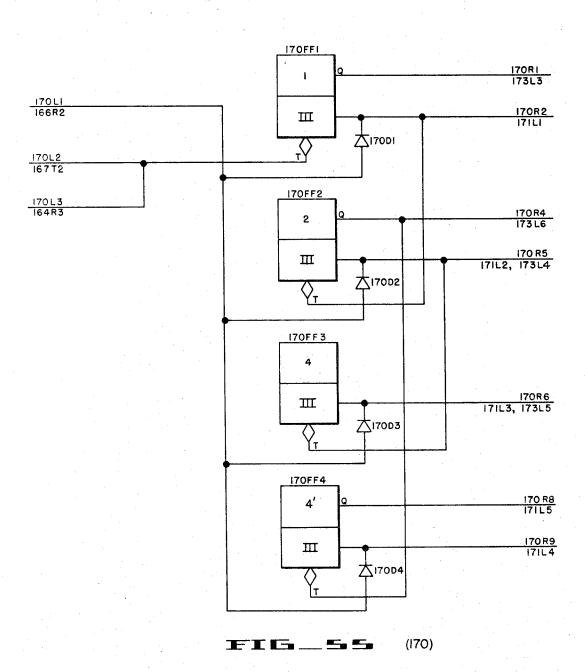

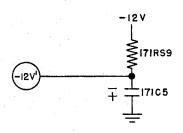

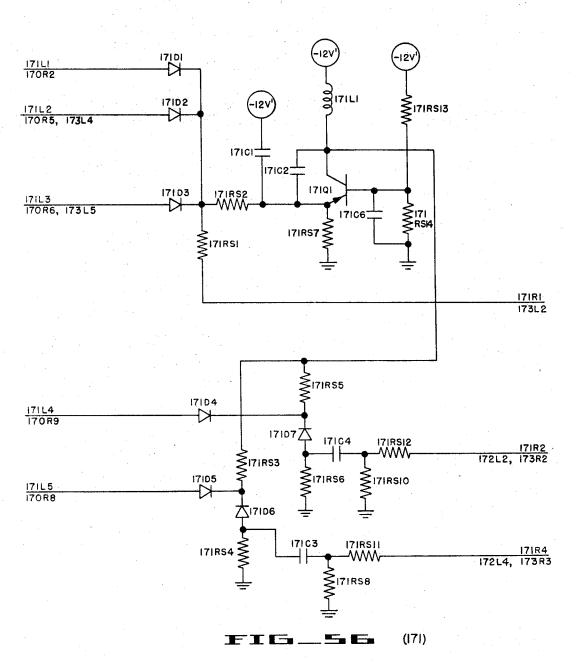

FIGURES 42 to 60 comprise a circuit diagram of the display in accordance with the present invention.

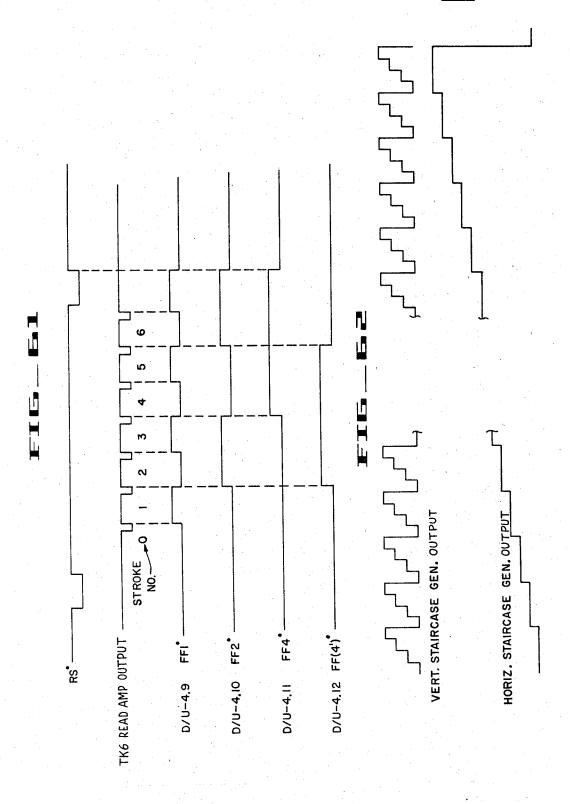

FIGURE 61 is a timing diagram of the operation of the segment flip flops of the display unit and a description of the timing signals obtained from the magnetic drum 60

track 6 read head circuit. FIGURE 62 is a pictorial description of the output signal of the vertical staircase generator and the horizontal staircase generator of the display device.

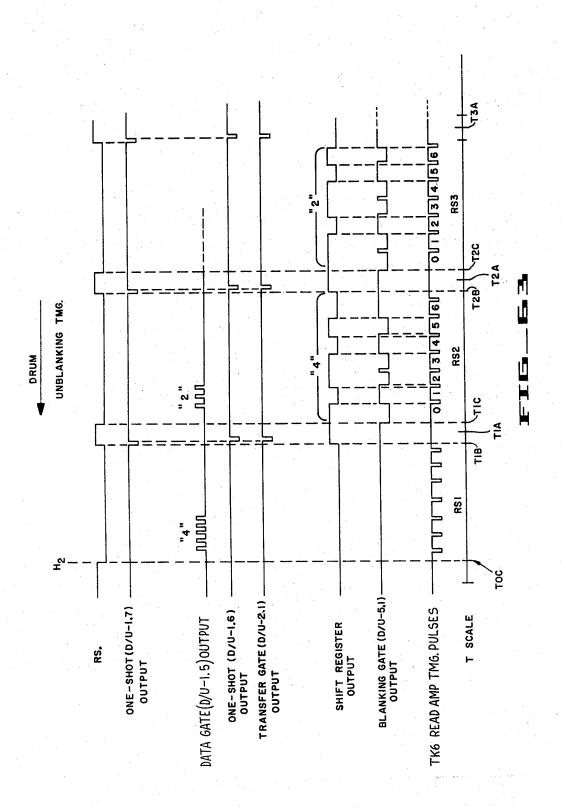

FIGURE 63 is a timing diagram of the unblanking cir- 65 cuitry of the display system.

FIGURE 64 is a diagram of a typical character raster produced on the face of the cathode ray tube of the dis-

signals of the segment flip flops of the display unit.

#### GENERAL SYSTEM

FIGURE 1A shows the display device in block diagram form. A first signal from oscillatory signal generator 10 75 time prior to the next H2 pulse.

is coupled through inhibit device 12 and combined with the output of weighted signal generator 14 in vertical mixer 16. The output of mixer 16, along with the signal from vertical staircase generator 18, are coupled to vertical amplifier 19 which provides the vertical deflection signal. A second output from oscillatory signal generator 10 is coupled through inhibit device 20 and combined with the output of weighted signal generator 22 in horizontal mixer 24. The output of mixer 24, along with the signal from horizontal staircase generator 26, are coupled to horizontal amplifier 28 which provides the horizontal deflection signal. The vertical and horizontal deflection circuits, including enable means 30, are under the control of timing and control unit 32. All the above elements are described in greater detail below.

#### **TIMING**

Since the operation of this display device is primarily dependent upon the timing therein, it is initially essential to understand the operation of the timing pulse generator system and, subsequently, the timing required for the performance of each operation of the display. The basic timing signals utilized in the display in accordance with the present invention are obtained from the magnetic tracks located on the drum of a calculator such as described in the application of Ragen, Ser. No. 398,902 filed Sept. 24, 1964. This subject matter is incorporated herein by reference.

FIGURE 1 sets forth the output of the read heads of tracks 1, 2 and 6 of the drum indicated as TK1, TK2 and TK6, respectively. It is assumed that the drum is rotating toward the left as indicated by the arrow in FIGURE 2. Track 1 produces H pulses, track 2 produces R pulses and track 6 produces dipslay pulses. Each pulse in FIGURE 1 represents a change in the state of the magentic materal on the drum, this change being sensed by the reading heads associated with the drum to produce a bit pulse.

Track 1 produces H pulses, these pulses comprising two individual pulses per revolution of the magnetic drum, these pulse bits being closely spaced on the drum as shown in FIGURE 2. The short space of time between these H pulses lettered H1 and H2 is referred to as "dead time" since no operations of the display circuit take place during this time period. Track 2 produces 101 equally spaced pairs of timing pulses positioned in time from T0B to T100C. These pulses are set forth in FIGURES 3 and 4 at the B and C times. It will be noted that B time occurs one half bit time prior to A time (the A times being equally spaced between B and C times) and the C time corresponding to the second bit of the R bit pair occurring one half bit time after an A time.

Track 6 produces display pulses, these pulses comprising seven spaced pulses appearing in the period slightly after a C time and before the following B time. Therefore, seven negative pulses will appear in the period just after T0C and before T1B of FIGURE 1. Also, seven such pulses will appear in the time period between T1C and T2B and so on for each of the one hundred time periods reprsented in FIGURE 1. These pulses are shown in more deail in FIGURES 62 and 63.

In summary, it can therefore be seen that in the operation of the drum, first an H1 pulse will appear, then there will be a short period of "dead time" when no operations occur. There will then be a first R pulse at time TOB (FIGURE 1) then, one bit later at TOC time, an H2 pulse and a second R pulse at time T0C. This is followed by 7 bit pulses occurring via track 6, these 7 bit pulses occurring in the time period from just after the T0C time until just prior to the next following T1B time. The ay unit.

Above time periods are set forth on the exemplary time FIGURE 65 is a table of the weighting of the output 70 scale T of FIGURE 1. This sequence will continue for one hundred such pulse groups about the track until time T100B has been reached, whereupon an H1 pulse and an R pulse are received and then a "dead time" returns until the following R pulse which occurs one bit

Referring now to FIGURE 5, the track therein is labelled track 4 of the magnetic drum and includes a space marked H which corresponds to the space between position H1 and H2 of track 2 or the "dead time." This space is not restricted as to size. Immediately upon occurrence of the H2 signal, the following track space, which corresponds to the portion of track 4 corresponding to times T0C to T1A of track T in FIGURE 1, is the area in which the least significant digit of a number to be stored in the temporary storage register No. 1 (T1) will be stored by the reading therein of a number of bits equal to the value of the number to be stored therein. As shown, the number "4" is stored therein. The portion of scale T corresponding to the time period from time T1A to time T2A, corresponds to the portion of track 4 labelled T2, this portion of track 4 being similar to register T1 and being utilized as a second temporary storage register. The portion of track 4 corresponding to track T in time T2A to T3A is referred to as the accumulator (ACC) whereas the portion of track 4 corresponding to times T3A to T4A is referred to as the entry register (ENT). Each of track portions T1, T2, accumulator register and entry register indicated as 1/1, 1/2, 1/3 and 1/4, repectively, will store the least significant digit of a number to be stored in the entire temporary register T1 or T2, accumulator register or entry register. During subsequent times as referred to in the T scale of FIGURE 1, track 4 will continue to include space for more significant digits of the storage register T1, storage register T2, accumulator register and entry register until at time T100A there will have been 25 of each of these registers. The registers set forth in track 4, as indicated supra, are referred to by utilization of two numbers located in each register block. the top number of which indicates the significance of the digit and the bottom number of which indicates the particular register, i.e., temporary storage register T1 (1), temporary storage register T2 (2), accumulator register (3) or entry register (4). A read head is positioned adjacent track 4 for reading therefrom.

diagram of the various timing signals provided by the timing circuitry of the display device. The T scale indicates the various time periods from T0C to T100A, identical to the T scale of FIGURE 1.

# H TIMING SIGNALS

The H signal shifts from the negative voltage level at time T0C to the positive voltage level and remains at the positive voltage level until time T100C when this signal then shifts back to the negative voltage level. This signal is indicated as H. It will be noted that the portion of the drum between the H1 and the following H2 signal is the "dead time" indicated in FIGURE 2.

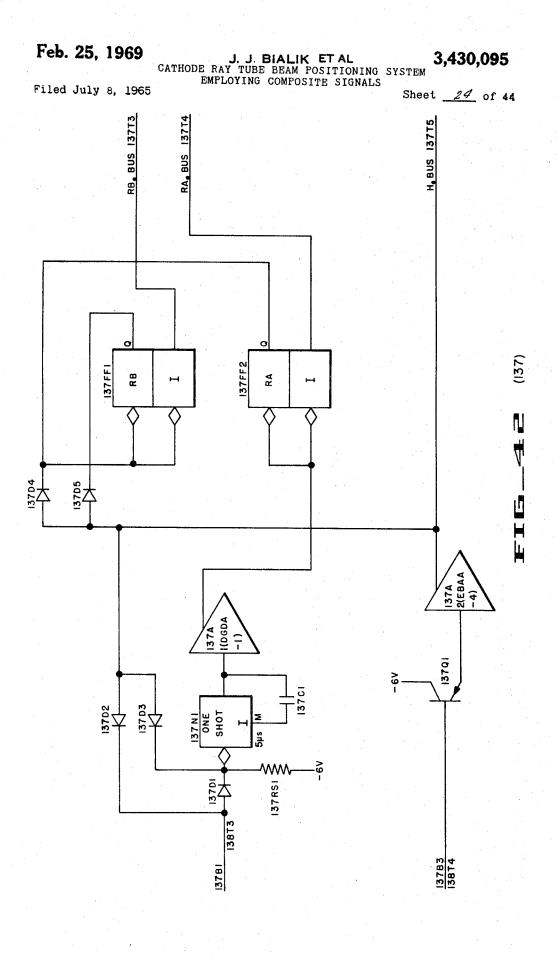

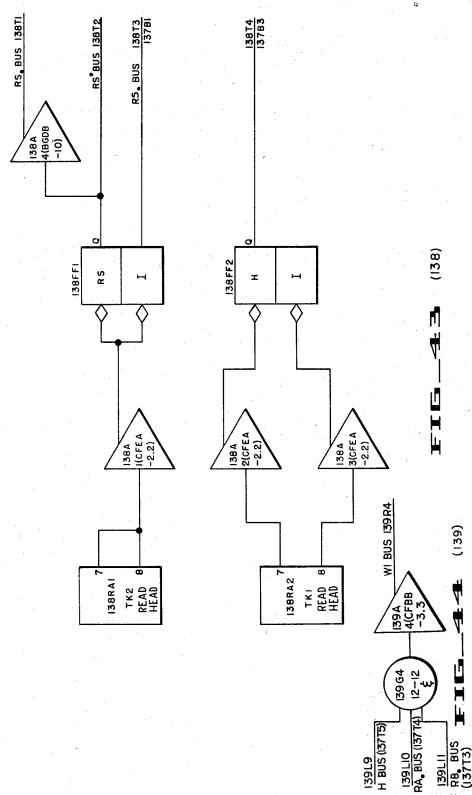

This H signal is provided by the circuitry set forth in FIGURE 43, wherein the H2 indication on track 1 on the drum is sensed by track 1 read head 138RA2 and transferred through inverters 138A2 and 138A3 to the input terminals of the H flip flop 138FF2. The input signal provided by inverter 138A2 is a positive-going pulse, also the signal provided by inverter 138A3 is a positive-going pulse. The positive-going pulse produced by inverter 138A2 is applied to the input of the flip flop 138FF2 and sets this flip flop, thereby providing negative voltage level signal on the H. bus 138T4. This signal will appear and will remain on bus 138T4 until the next following H2 pulse which will reset the H flip flop 138FF2 and invert the voltage level on this bus. The output on the bus 138T4 passes through the emitter follower 137Q1 and is inverted by the inverter 137A2 to provide an H signal on the output bus 137T5.

# RS TIMING SIGNALS

The negative voltage level RS signal is obtained on bus 138T3 100 times during each revolution of the drum from time T0C to T1B, T1C to T2B . . . T99C to T100B as indicated in FIGURE 6. It will be noted that the first RS. 75 RB flip flops. The voltage levels on these buses 137T1

signal commences at time T0C by going, at that time, from a positive voltage level to a negative voltage level and remaining in this negative state until the next following B time whereupon this signal reverts to its positive voltage level until the next following C time whereupon this signal again reverts to its negative level. This cycle commences for 100 T periods. Similarly, the positive voltage level RS signal on bus 138T2 is identical in all respects to the RS signal on bus 138T3 except that this signal goes from a negative voltage level to a positive voltage level at the identical times that the RS signal on bus 138T3 goes from a positive voltage level to a negative voltage level and vice versa.

These RS signals are obtained by reading the signals from track 2 as shown in FIGURE 1 with the track 2 reading head 138RA1 (FIGURE 43), these signals being inverted in the inverter 138A1 and transferred to the complement inputs of the RS flip flop 138FF1. Upon reading the signal on track 2 corresponding to the B time of FIG-URES 3 and 4, the RS flip flop 138FF1 is set by a positive-going voltage pulse thereto, and provides a negative voltage level output on RS bus 138T2. Simultaneously, a positive voltage level signal is applied to the RS bus 138T1 through inverter 138A4. When the following bit pulse taken from track 2, which corresponds to the time C of FIGURES 3 and 4, is received from track 2 read head, this signal will provide a second positive-going voltage level and reset the RS flip flop. Thereby, the voltage levels on the RS buses 138T1 and 138T2 are inverted to provide significant voltage levels on these buses only in the time period between a C time and the following B time on the drum.

#### W TIMING SIGNAL

The pulses on bus 138T3 (FIGURE 43) are transferred through a diode 137D1 (FIGURE 42), a time delay one shot 137N1, and the inverter 137A1 to the complement inputs of the RA flip flop 137FF2. This RA flip flop, along with the RB flip flop 137FF1, comprises a binary counter Referring now to FIGURE 6, there is shown a timing 40 with four states. Therefore, for each positive-going transition on the RS flip flop RS bus, there will be a corresponding change in state of the counter composed of the RA and RB flip flops. It can be seen that the RA and RB flip flops are initially both in the reset condition due to a positive-going transition resetting signal applied on the H bus 137T5. This positive voltage level on the bus 137T5 disables the one shot 137N1 through diode 137D3 by holding the one shot input at a positive voltage level.

It should be noted that the H flip flop 138FF2 and the RS flip flop 138FF1 are synchronized by the positive voltage level on bus 137T5, which level is applied through the diode 137D2 to the RS bus 138T3, thereby setting the RS flip flop for time synchronization with the H flip flop. When the voltage level on the H bus 137T5 then goes to a negative voltage level, the RA, RB and RS flip flops and the one shot 137N1 are unlocked.

Concurrently with the unlocking of the RS, RA and RB flip flops and the one shot 137N1, an input signal to the RS flip flop 138FF1 resets this flip flop, this resetting having no effect on the timing circuitry. At time T1B, a positive-going transition to the complement input of the RS flip flop 138FF1 sets this flip flop and provides a positivegoing transition on the RS output bus thereof. This positive-going transition is delayed in the one shot 137N1, the negative-going output therefrom being inverted by the inverter 137A1 and setting the RA flip flop 137FF2 at time T1A. At time period T1C, a positive-going transition to the input of the RS flip flop 138FF1 will reset this flip flop, producing a negative level on the RS, bus, this negative level having no effect as before. This procedure is continued for each T time to thereby step the counter composed of the RA and RB flip flops and provide various significant voltage levels on the buses 137T1 through 137T4 in accordance with the condition of the RA and

through 137T4 will aid in providing the W timing signals as will be described hereinbelow.

The RA and RB signals are utilized to provide the W1 signal on the bus 139R4 in the display. As shown in FIGURE 6, the W1 signal remains in its negative voltage level condition except during times indicated as T1, i.e., the time period between times T0C and T1A, the time period between times T4A and T5A, . . . It will be seen that this W1 pulse is provided at every fourth time period beginning with time T0C. It should also be noted that the W1 pulse extends in time from a first A time to the next succeeding A time as shown in FIGURE 3 for all time periods except T0. This extended range is provided by the time delay obtained in the one shot 137N1 since the RA and RB counter advances during the positive-going portion of the RS signal on bus 138T3.

It can now be seen that, in the time period between time T0C to T1A, the H bus 139L9 will have a significant negative voltage level signal thereon as explained supra and shown in FIGURE 6. Also, since at time T0C the RA and RB flip flops 137FF1 and 137FF2 will both be in the reset state and thereby provide a negative voltage level output signal on the RA bus 137T4 and 139L10 and a negative voltage level signal on the RB bus 137T3 and 139L11. Accordingly, at this time and the AND gate 139G4 is enabled and provides a negative voltage output therefrom, this negative voltage level being inverted by inverter 139A4 to provide a positive voltage level output on the W1 bus 139R4.

At time T1B, the RS flip flop is set and applies a delayed positive-going signal through the one shot 137N1 to set the RA flip flop 137FF2 at time T1A. Accordingly, at this time, the RB bus 137T3 will remain in its negative voltage condition whereas, the RA bus 137T4 and 139L10 have now changed from a negative voltage level condition to a poistive voltage level condition, thereby disenabling the

AND gate 139G4.

The next positive-going transition on the bus 138T3, as before, will again change the count of the RA and RB flip flops by "1" and, accordingly, the RA buses 137T4 and 139L10 will be at a negative voltage level, and the RB buses 137T3 and 139L11 will be at a positive voltage level.

At the next positive-going transition of the RS signal on bus 1388T3, as before, the counter composed of flip flops 137FF2 and 137FF1 will again change in count 45 by "1," etc.

Accordingly, as set forth supra, each of the W1 timing signals required is obtained at its proper time by means of the above described circuitry as clearly set forth in FIGURE 6.

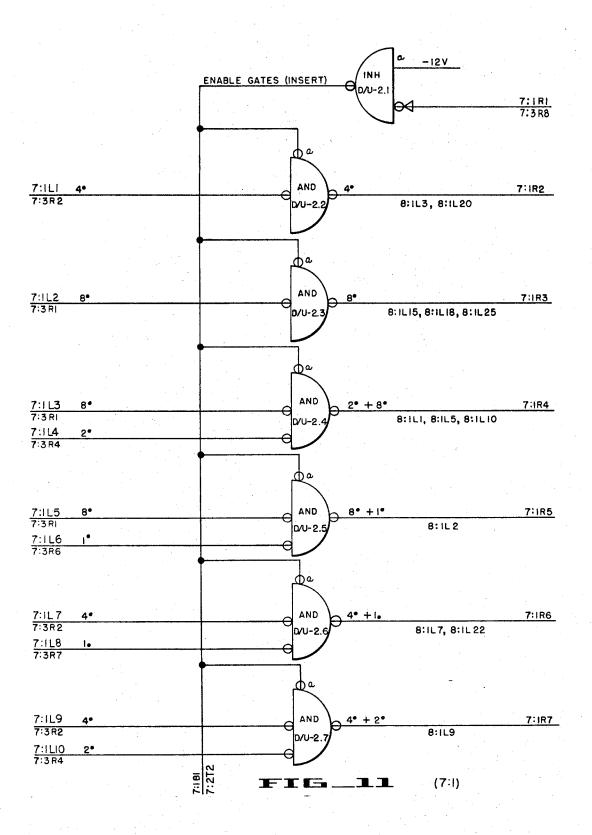

The preferred embodiment of the invention will first be described with reference to the logic diagrams thereof wherein the display is depicted by logical circuitry. These diagrams comprise FIGURES 10 to 17.

#### CONVENTIONS

It is necessary to understand certain conventions that are utilized herein. In FIGURE 7, e.g., is shown a symbolic diagram of a flip flop as used in the logical circuitry herein. The flip flop comprises terminals numbered from 60 10 to 21. The output terminals are numbered 11 and 12 and will be referred to as the FF and FF output terminals, respectively. As noted in the table, a binary "1" or set condtion exists when a negative voltage level appears on the FF output terminal (about -6 volts) and 65 a positive voltage level appears at the FF output terminal (about 0 volts). It follows that the flip flop will be set when the FF output terminal thereof is at a positive voltage level and the FF output terminal thereof is at a negative voltage level. At some places herein the FF terminal 70 is designated Q, or a; and the FF terminal is designated non-Q, or b.

Referring now to FIGURE 8, taken in conjunction with FIGURE 7, there are noted the various symbols utilized and the definitions thereof. The transfer symbol is lo- 75

cated on the flip flop of FIGURE 7 at terminals 14, 15 and 21 thereof. These three symbols always occur together and are defined to indicate that the impressing of a positive-going voltage transition on terminal 14 will transfer the voltages on the terminals 15 and 21 respectively to the terminals 12 and 11. That is, if a negative voltage is located on terminal 21 and a positive voltage is located on terminal 15, the application of a positive-going transition on terminal 14 will set the flip flop, or, in other words, place a negative voltage level at the FF- output terminal and a positive voltage level at the FF output terminal thereof. Of course, if the flip flop is already set, no change will take place. Also, if the terminals 15 and 21 each have a negative signal thereon, no change will take place.

The symbol on terminals 17 and 20 indicates that the occurence of a positive-going transition on one of the said terminals will reset the flip flop. The symbol on terminals 19 and 16 indicate that the occurrence of a positive-going transition on one of the said terminals will set the flip flop. The symbol on terminal 18 indicates that the occurence of a positive-going transition on this terminal will complement the flip flop, i.e., change the state of the flip flop from the set condition to the reset condition or from the reset condition to the set condition, depending upon the initial condition of the flip flop.

The symbol on terminal 10 of the flip flop indicates that the placement of a positive voltage level thereon will reset the flip flop. The symbol on terminal 13 of the flip flop indicates that the placement of a positive voltage level thereon will set the flip flop. The above symbols and the other symbols set forth in FIGURE 8 can be used to depict each of the operations of the flip flops utilized in

the display to be described hereinafter.

The symbols set forth in FIGURE 8 are also utilized to depict the various gate circuits utilized in the present invention. The gate circuits set forth in FIGURES 10 to 17 are labelled as either AND gates or OR gates. The symbols at the input and output terminals are defined to indicate the type of input and output terminals are defined to indicate the type of input required to provide the designated output. That is, assuming an AND gate, if all input terminals thereto are provided with the negative level symbol of FIGURE 8 and the output terminal thereof is provided with the positive level symbol of FIGURE 8, the symbology states that if a negative level is applied to all input terminals of the gate (AND function) then a positive voltage level will appear at the output terminal thereof. If the gate under consideration is an OR gate having the positive level symbol on the input terminals thereto and a negative level symbol on the output terminal therefrom, the symbology states that if a positive level is applied to at least one of the input terminals thereof (OR function) then a negative voltage level will appear at the output terminal thereof. Other types of gate configurations utilizing the above explained symbology can also be utilized.

The symbology set forth in FIGURE 8 can be used in many other situations. This symbology, when tied to a bus legend, will indicate the signal required on that bus for the bus function to be performed. This symbology is also utilized at the input and output terminals of other types of circuits to indicate the output obtained when a particular input signal is applied thereto. This type of symbology is depicted in FIGURE 9, wherein a one shot is set forth, the symbology indicating that a positive-going transition signal at the input thereto will provide a posi-

tive level at the output terminal thereof.

It should be understood that various combinations of the signal symbols set forth in FIGURE 8 can be used, each symbol indicating the function defined thereby.

In the labelling of all buses, the numbers above the bus indicate bus number designation, whereas numbers below the bus indicate continuing portions of the bus. The numbers utilized to designate buses include a first

number and a second number after a colon indicating the sheet of drawing as marked in parentheses on said sheets, a letter (T, B, L, R) indicating the top, bottom, left or right side of the sheet and a number indicating the bus designation on the sheet. For example, a bus marked 10:1R7 describes a bus on FIGURE 16 (sheet 10:1) leaving this figure from the right and being the seventh bus down from the top.

With the above conventions and positioning of the figures in mind, the display will now be described in 10 detail with respect to the logic diagram as set forth in FIGURES 10 to 17.

The following is a description of the operation of a preferred embodiment of the display system which can be utilized with a calculator or a like device capable of pro- 15 viding digital information indicative of indicia to be displayed.

The content of each of the storage regsters on track 4 of the drum (FIGURE 5) will be constantly displayed by the display device. The content of each register is dis-20 played on a separate row on the face of a cathode ray tube, thereby indicating the contents of each element of the individual registers, i.e., the entry register, the accumulator register, the temporary storage register No. 1 and the temporary storage register No. 2.

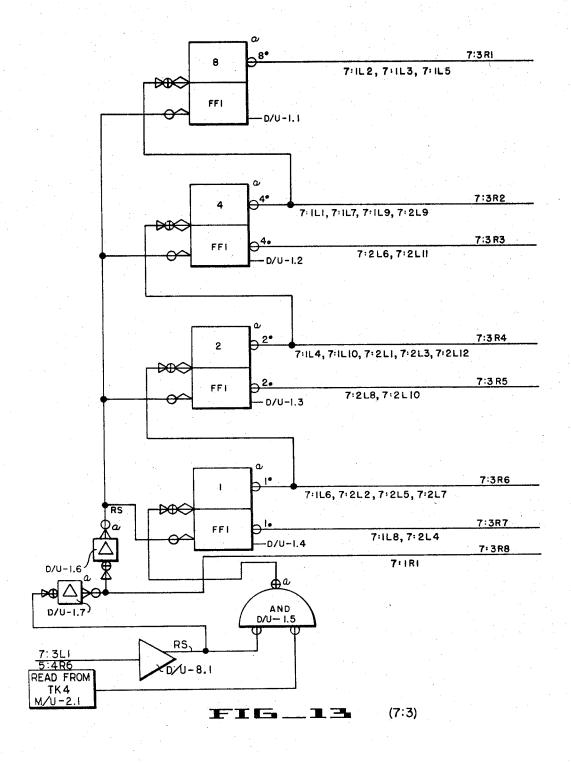

We assume that the track 4 read head M/U-2.1 (FIG-URE 13) is initially at the trailing edge of the dead time portion of track 4, and is about to commence reading of data stored in the first or least significant digit position of the temporary storage register No. 1. This section of 30 the temporary storage register No. 1 is indicated by the numbers 1/1 of track 4 in FIGURE 5.

As the track 4 read head passes over the first section (1/1) of the temporary storage register No. 1, all bits stored therein will be read and, for each bit read, a pulse 35 will be obtained having a negative-going transition, this negative-going transistion being applied to the input terminal of the AND gate D/U-1.5. The concurrence of a positive level on the RS bus 7:3L1 inverted by the inverter D/U-8.1, and the negative-going transition from 40 the track 4 read head will enable AND gate D/U-1.5 and provide a positive-going transition at the output thereof, this positive-going transition being applied to the complement input of the No. 1 flip flop of a display entry counter composed of flip flops D/U-1.1 to D/U1.4. All subsequent negative-going transitions on the track 4 read bus 7:3L2 will provide additional positive-going transitions at the output of the AND gate D/U-1.5 and thereby continually set the display entry counter to provide an indication of the number stored in the first section of the temporary storage register No. 1. It will be noted that the count obtained from the temporary storage register No. 1 herein will include the "excess" bit (an integer being represented by a number of bits equal to the integer plus one) and, therefore, the count obtained in the entry counter of the display circuit will be one greater than the number to be ultimately displayed on the display device. This excess bit is merely used by choice, it being understood that almost any code configuration could be utilized.

The flip flops of the display entry counter are, therefore, either in their set or reset condition to indicate the digit read from the element 1/1 temporary storage register No. 1. This reading into the display entry counter takes place during the time period beginning at T0C and ending at T1B, this being the first RS period as shown on FIGURE 63. At the end of the first RS time period, the negative-going transition on the RS bus 7:3L1 is inverted and applied to the input of a one shot D/U-1.7, a negative-going pulse being developed at the output of this one shot. This negative-going pulse is applied over the bus 70 7:3R8 to the bus 7:1R1, this bus being an input terminal of the inhibit gate D/U-2.1, the other input to this gate being a negative voltage level signal. The concurrence of this negative voltage level signal and a negative-going

this gate D/U-2.1 and produce a negative voltage level at the output thereof. This negative voltage level is applied to one of the input terminals of each of the AND gates D/U-2.2 to D/U-2.13 of FIGURES 11 and 12. Each of these AND gates D/U-2.2 to D/U-2.13 will provide a negative voltage level output thereat if each of the input terminals thereto is at a negative level. The input terminals of these AND gates are directly connected to the output terminals of the entry counter flip flops D/U-1.1 through D/U-1.4 (FIGURE 13).

It can be seen that the FF output of the No. 8 flip flop D/U-1.1 of the display entry counter is applied via the bus 7:3R1 to the sole input of AND gate D/U-2.3, an input of the AND gate D/U-2.4, an input of the AND gate D/U-2.5.

The output of the FF output terminal of the No. 4 flip-flop of the display entry counter is transferred along the bus 7:3R2 to an input terminal of the AND gate D/U-2.6, and the AND gates D/U-2.7, D/U-2.12 and the only input of D/U-2.2.

The output signal on the FF output terminal of the No. 4 flip-flop D/U-1.2 of the entry counter provides a signal on the bus 7:3R3, this signal also appearing at the input terminal of the AND gates D/U-2.10 and D/U-25 **2.13**.

The FF output of the No. 2 flip flop D/U-1.3 of the display entry counter provides a signal along the bus 7:3R4 to the AND gates D/U-2.4, D/U-2.7, D/U-2.8, D/U-2.9 and D/U-2.13.

The FF output of the No. 2 flip flop DU/-1.3 of the display entry counter provides a signal on the bus 7:3R5, this signal being applied to an input terminal of the AND gates D/U-2.11 and DU/-2.12.

The FF output terminal of the No. 1 flip flop D/U-1.4 of the display entry counter provides a signal along the bus 7:3R6 to an input terminal of AND gates D/U-2.5, D/U-2.8, D/U-2.10 and D/U-2.11.

The FF output terminal of the No. 1 flip flop of the display entry counter D/U-1.4 provides a signal along the bus 7:3R7 to an input terminal of the AND gates D/U-2.6 and D/U-2.9.

At the end of the RS period, the RS bus 7:3L1 will have a negative-going transition thereon, this negativegoing transition being inverted by the inverter D/U-8.1 (FIGURE 13) and applied to the input of the one shot D/U-1.7. The one shot D/U-1.7 provides an inverted negative-going transition at the output thereof. The negative-going transition has no effect on the one shot D/U-1.6. After a short delay, the output from one shot D/U-1.7 reverts to a positive voltage level to provide a positive-going transition at the input of one shot D/U-1.6.

This output from the one shot D/U-1.7 is delayed and inverted by one shot D/U-1.6 to provide a negative-going transition at the output thereof to reset the flip flops D/U-1.1 to D/U-1.4 inclusive after the information has been read into the shift register D/U-3.1 to D/U-3.7 inclusive (to be explained hereinafter).

Prior to resetting of the entry counter, the AND gates (FIGURES 11 and 12) are enabled by a negative voltage level at the output terminal of inhibit circuit D/U-2.1 provided by the negative-going transition at the output of one shot D/U-1.7. It can be seen by an inspection of the input terminals of the AND gates D/U-2.2 through D/U-2.13 that the AND gate D/U-2.2 will provide a negative voltage level at the output thereof when the No. 4 flip flop of the display entry counter is in the set condition. The AND gate D/U-2.3 will provide a negative voltage level at the output thereof when the No. 8 flip flop of the display entry counter is in the set condition. The AND gate D/U-2.4 will provide a negative voltage level at the output thereof when both the No. 8 flip flop and the No. 2 flip flop of the display entry counter are in the set condition. The AND gate D/U-2.5 will provide a negative voltage level at the output thereof when both the No. 8 transition on the input bus thereto 7:1R1 will enable 75 and the No. 1 flip flops of the display entry counter are

in the set condition. The AND gate D/U-2.6 will provide a negative voltage level at the output thereof when the No. 4 flip flop of the display entry counter is set and the No. 1 flip flop thereof of this counter is reset. The AND gate  $D/\bar{U}$ -2.7 will provide a negative voltage level at the output thereof when both the No. 4 flip flop and the No. 2 flip flop of the display entry counter are in the set condition. The AND gate D/U-2.8 provides a negative voltage level at the output thereof when both the No. 2 and the No. 1 flip flops of the display entry counter are in the set condition. The AND gate D/U-2.9 provides a negative voltage level at the output thereof when the No. 2 flip flop of the display entry counter is in the set condition and the No. 1 flip flop thereof is in the reset condition. The AND gate D/U-2.10 provides a negative voltage level at the output thereof when the No. 1 flip flop of the display entry counter is in the set condition and the No. 4 flip flop thereof is in the reset condition. The AND gate D/U-2.11 provides a negative level at the output thereof when the No. 1 flip flop of the display entry counter is in the set condition and the No. 2 flip flop thereof is in the reset condition. The AND gate D/U-2.12 provides a negative voltage level at the output thereof when the No. 4 flip flop of the display entry counter is in the set condition and the No. 2 flip flop thereof is in the reset condition. The AND gate D/U-2.13 provides a negative voltage level at the output thereof when the No. 4 flip flop of the display entry counter is in a reset condition and the No. 2 flip flop thereof is in the set condition.

It can be seen from an inspection of the above and FIGURES 11 and 12 that each of the respective buses 7:1R2 to 7:1R7 and 7:2R1 to 7:2R6 will have a negative voltage level thereon when their associated AND gates have been properly enabled.

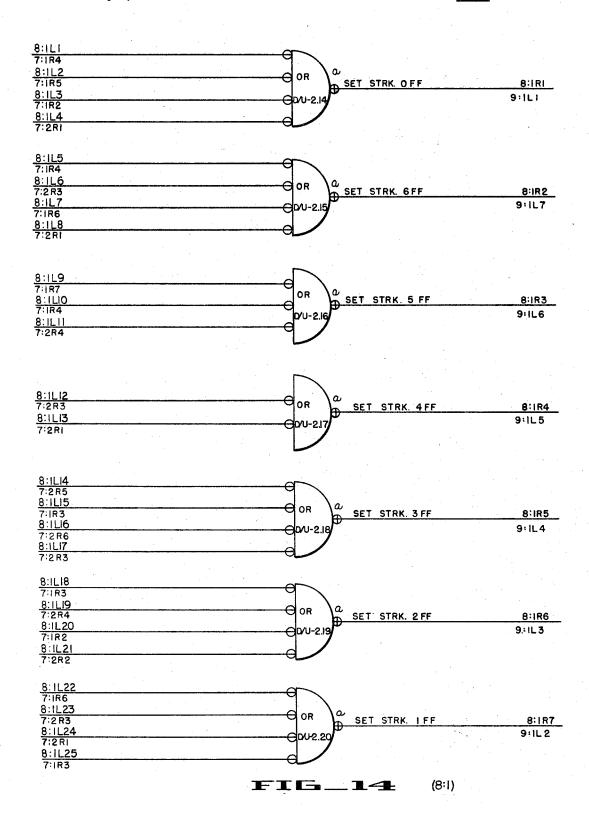

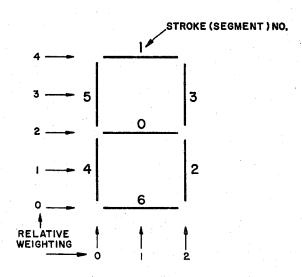

It should, at this point, be understood that the characters to be displayed are produced from a scanning raster designed to scan a figure "8." This raster is displayed in FIGURE 64 wherein the figure "8" is composed of a plurality of stroke segments numbered from 0 through 6. Each of the possible characters to be displayed on the face of the cathode ray tube is composed of certain ones of these stroke segments and, therefore, in order to properly display a particular character, it is only necessary to suppress the display of certain ones of the strokes.

Suppression of the undesired strokes is accomplished by means of the OR gates D/U-2.14 through D/U-2.20 of 45

The OR gate D/U-2.14 is coupled to the output terminal of the AND gates D/U-2.2, D/U-2.4, D/U-2.5 and D/U-2.8. Therefore, when a negative voltage level appears at the output terminal of any of the above-men- 50 tioned AND gates coupled to an input of the OR gate D/U-2.14, a positive voltage level will appear at the output of this OR gate on set stroke zero flip flop bus 8:1R1.

The OR gate D/U-2.15 provides a positive voltage level at the output thereof on the set stroke 6 flip flop bus 55 8:1R2 when at least one of the AND gates D/U-2.4, D/U-2.6, D/U-2.8 or D/U-2.10 has a negative voltage level at the output thereof.

The OR gate D/U-2.17 provides a positive voltage level at the output thereof on the set stroke 5 flip flop bus 60 8:1R3 when a negative voltage level is provided at the output terminal of one of the AND gates D/U-2.4, D/U-2.7 or D/U-2.11.

The OR gate D/U-2.7 provides a positive voltage level on the set stroke 4 flip flop bus 8:1R4 when a negative 65 voltage level appears at the output of one of the AND gates D/U-2.8 or D/U-2.10.

The OR gate D/U-2.18 provides a positive voltage level on the set stroke 3 flip flop bus 8:1R5 when a negative voltage level appears at the output terminal of one of 70 the AND gates D/U-2.3, D/U-2.10, D/U-2.12 or D/U-2.13.

The OR gate D/U-2.19 provides a positive voltage level at the output thereof on the set stroke 2 flip flop output terminal of one of the AND gates D/U-2.2, D/U-2.3, D/U-2.9 or D/U-2.11.

The OR gate D/U-2.20 provides a positive voltage level on the output thereof on the set stroke 1 flip flop bus 8:1R7 when a negative voltage level appears at the output terminal of one of the AND gates D/U-2.3, D/U2.6, D/U-2.8 or D/U-2.10.

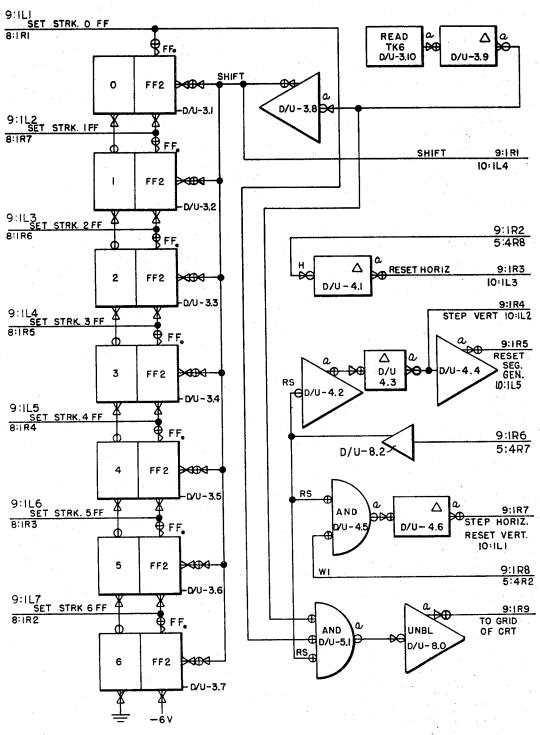

The signal levels on the buses 8:1R1 to 8:1R7 operate the shift register flip flops D/U-3.1 to D/U-3.7 (FIGURE 15) in the following manner:

The output voltage level signal on the bus 8:1R1 will be applied to the FF output lead of the zero flip flop D/U-3.1 (FIGURE 15) along the set stroke zero flip flop bus 9:1L1. Similarly, the output voltage level on the bus 8:1R2 will be applied to the FF output lead of the No. 6 flip flop D/U-3.7; the output voltage level on the bus 8:1R3 will be applied to the bus 9:1L6, this being the FF output terminal of the No. 5 flip flop D/U-3.6; the output voltage level on the bus 8:1R4 will be applied to the set stroke 4 flip flop bus 9:1L5, this being the FF output terminal of the No. 4 flip flop D/U-3.5; the output voltage level on the set stroke 3 flip flop bus 8:1R5 will be applied to the set stroke 3 flip flop bus 9:1L4, this being the FF. output terminal of the No. 3 flip flop D/U-3.4; the output voltage level on the set stroke 2 flip flop bus 8:1R6 being applied to the set stroke 2 flip flop bus 9:1L3, this being the FF output terminal of the No. 2 flip flop D/U-3.3; and the output voltage level on the set stroke 1 flip flop bus 8:1R7 will be applied to the set 30 stroke 1 flip flop bus 9:1L2, this bus being the FF output terminal of the No. 1 flip flop D/U-3.2.

Thus, when the output voltage level on one or more of the buses 8:1R1 to 8:1R7, as provided by the output signals from the OR gates of FIGURE 14, has a positive going transition thereon, the associated flip flops of the display shift register (FIGURE 15) will be set.

During each of the RS time periods, a series of seven negative-going pulses is generated in response to information on track 6 of the drum (FIGURE 1), these pulses being provided by the track 6 read head D/U-3.10 (FIG-URE 15). These negative-going pulses are inverted in the amplifier forming part of D/U-3.10 and then pass through the one shot D/U-3.9 and appear at the output thereof as negative-going transitions. These negative-going transitions which are delayed by the one shot, are then inverted by the inverter D/U-3.8 to provide positive-going transitions on the shift bus, this bus being coupled to the transfer terminal of each of the flip flops of the shift register D/U-3.1 through D/U-3.7.

This transfer input terminal of the flip flops D/U-3.1 to D/U-3.7 will transfer the levels from the input terminals thereof to the output terminals thereof when a positive-going transition is applied thereto. In this manner, the content of the shift register is shifted completely therethrough by the 7 positive-going transitions applied to the transfer input of the flip flops thereof by the track 6 read head (FIGURE 61).

A positive-going transition appears at the output of the one shot D/U-3.9 at the trailing edge of a pulse produced from track 6, this positive-going transition being applied to one of the input terminals of the AND gate D/U-5.1 (FIGURE 15). This AND gate is enabled by the concurrent positive level input provided by the inverter D/U-8.2 which inverts a negative voltage level on the RS bus 9:1R6 and a positive level on the set stroke zero flip flop bus 9:1L1. It can be seen that the level on the set stroke zero flip flop bus 9:1L1, which is applied to the input of the AND gate D/U-5.1, will depend upon the condition at that particular time of the zero flip flop of the shift register D/U-3.1. A set condition of this flip flop will provide a positive level on the FF output thereof and thereby provide an enabling signal for the AND gate D/U-5.1. However, the absence of a set condition, i.e., a reset conbus 8:1R6 when a negative voltage level appears at the 75 dition of flip flop D/U-3.1, will provide a negative level

on the FF output terminal thereof and thereby disenable the AND gate D/U-5.1.

The condition of the AND gate D/U-5.1 determines whether or not an unblanking pulse will be provided to the grid of the cathode ray display tube D/U-7.0 (CRT) (FIGURE 17). The unblanking signal is provided, as explained supra, by the concurrent positive levels at the input terminals of AND gate D/U-5.1, thereby providing a negative output level therefrom, this output level being inverted by the inverter D/U-8.0 (FIGURE 15) to provide a positive level to the grid of the cathode ray tube along the bus 9:1R9. Conversely, it can be seen that the disenabling of AND gate D/U-5.1 will provide a positive output level therefrom and, it follows, that a negative output level will be provided on the bus 9:1R9, thereby cut- 15 ting off the grid voltage for the CRT and blanking same during that particular stroke time period.

The significant voltage levels on the set stroke zero flip flop bus 9:1L1 (FIGURE 15), which are provided at the input terminal of the AND gate D/U-5.1, are obtained 20 in the following manner: after the flip flops of the shift register have been initially set by the OR gates D/U-2.14 to D/U-2.20 in the manner explained hereinabove, succeeding positive-going transitions applied to the transfer inputs of the shift register flip flops D/U-3.1 to D/U-3.7 25 will successively shift the output voltage on the output terminals of any one of these flip flops to the next following flip flop of descending order. That is, the output voltage on the FF and FF terminals of the No. 6 flip flop D/U-3.7 will be shifted to the output terminals of 30 the No. 5 flip flop D/U-3.6 by the first positive-going transition on the transfer terminal of the No. 6 flip flop. Similarly, the output voltages from the No. 5 flip flop will be transferred to the No. 4 flip flop; the output voltage from the No. 4 flip flop will be transferred to the No. 3 flip flop; the output voltage from the No. 3 flip flop will be transferred to the No. 2 flip flop; the output voltage from the No. 2 flip flop will be transferred to the No. 1 flip flop and the output voltage from the No. 1 flip flop will be transferred to the zero flip flop. Accordingly, for each 40 successive positive-going transition on the transfer inputs of the shift register flip flops, the contents thereof will be shifted upward to the next succeeding flip flop for each incoming positive-going voltage transition.

It can be seen that the shift register will be completely 45 reset after 7 positive-going transitions have been applied to the transfer inputs thereof. This is caused by the fixed voltage levels at the input terminals of the No. 6 flip flop D/U-3.7. The first positive-going transition to the transfer terminal of this No. 6 flip flop will reset this flip flop due 50 to the voltage levels at the input terminals thereof, this reset condition being transferred upward to each of the succeeding flip flops until, after 7 such transitions, all of the flip flops will be reset in the manner described supra

for shifting the signals in the shift register.

In the manner described supra, it can be seen that the cathode ray tube grid circuit 9:1R9 will be enable during certain predetermined time periods only, these time periods being determined by the condition of the shift register prior to the application of the transfer signals 60 thereto.

It is also necessary to locate the cathode ray tube beam in the particular area thereof at a particular period in time.

Individual characters are positioned by the application 65 of horizontal and vertical incremental changes in sweep voltage. The appearance of these wave forms is similar to a stair step configuration (FIGURE 62).

There are 4 horizontal tracks displaced on the face of the cathode ray tube. The bottom-most track is a display 70 of the contents of the entry register, the next track is a display of the contents of the accumulator register, the next track is a display of the contents of the temporary storage register No. 2 and the topmost track

register No. 1. It can therefore be seen that, in order to display, first, the contents of the least significant portion of the temporary storage register No. 1, then the contents of the least significant portion of the temporary storage No. 2, then the contents of the least significant portion of the accumulator register, and then the contents of the least significant portion of the entry register, it is necessary that the position of the cathode ray tube beam be positioned vertically downward by one track level after reading of each section of each of the registers. That is, after the least significant digit of the temporary storage register No. 1 has been displayed, the cathode ray tube beam will be positioned vertically downward to the next track position and the contents of the least significant digit position of the temporary storage track No. 2 will there be displayed. The cathode ray tube beam will then be positioned vertically downward to the next level, whereupon the contents of the least significant digit position of the accumulator register will be displayed and, then, the cathode ray tube beam will again be positioned vertically downward to the bottom most track, whereupon the contents of the least significant digit position of the entry register will be displayed. This process continues with the beam being shifted horizontally by one digit position and vertically back to the topmost row, whereupon the vertical scanning cycle continues ad infinitum until the entire contents of each digit section of the registers have been displayed.

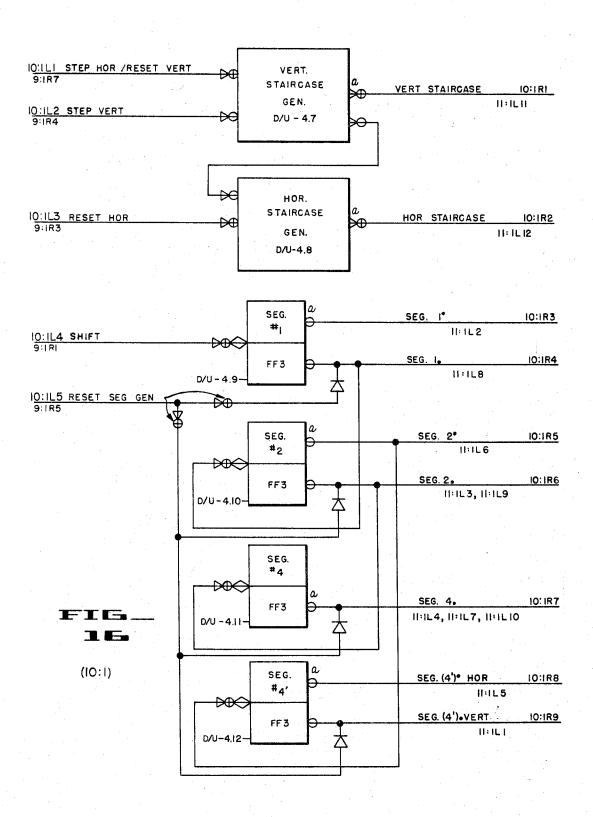

The above is accomplished in the following manner: The voltage waveform necessary to effect a change in the vertical position of a cathode ray tube beam is developed by the vertical staircase generator circuit D/U-4.7 (FIGURE 16). This circuit receives a negativegoing input signal at the end of each RS period. This negative-going voltage level is obtained when the RS bus 9:1R6 (FIGURE 15) goes positive, thereby providing a negative-going output from the inverter D/U-8.2 and a positive-going output from the inverter D/U-4.2. This positive-going output is delayed and inverted by the one shot D/U-4.3 to provide a negative-going output on the step vertical bus 9:1R4. This step vertical signal is applied to the step vertical bus 10:1L2, this bus being an input terminal of the vertical staircase generator D/U-4.7 (FIGURE 16).

These input pulses at the end of each RS period are received by the vertical staircase generator and, through a voltage build-up of a capacitor circuit therein, a voltage waveform is built up, causing the required deflection of the election beam in the cathode ray tube (see FIGURE 62). At the end of every fourth RS time period, a positive-going signal is produced on the step horizontal and reset vertical bus 10:1L1 by the next succeeding positive voltage level W1 timing signal on bus 9:1R8. This signal, in conjunction with a positive RS signal on RS bus 9:1R6, inverted by inverter D/U-8.2, resets the vertical staircase generator D/U-4.7 and, thereby, introduces one step into the horizontal staircase generator D/U-4.8. This single pulse input to the horizontal staircase generator will properly position the succeeding digit position in the horizontal display, this procedure continuing as shown in FIGURE 62.

As explained supra, the vertical staircase generator D/U-4.7 is advanced one step by storing a voltage in a capacitive circuit, this voltage being applied by negativegoing transitions applied along the step vertical buses 9:1R4 and 10:1L2. At the following W1 time period, one of the input terminals of the AND gate D/U-4.5 will have a positive voltage level on the W1 input terminal thereof, this terminal being the W1 bus 9:1R8. When the RS bus 9:1R6 goes positive, a positive-going transition will be applied at the output of AND gate D/U-4.5 due to the concurrence of positive signals at the input thereof, this positive-going transition being delayed by the delay circuit D/U-4.6 and appearing on the is a display of the contents of the temporary storage 75 step horizontal reset vertical bus 9:1R7. This positivegoing transition is applied to the step horizontal/reset vertical bus 10:1L1 to reset the vertical staircase generator and step the horizontal staircase generator to its next position. It is noted that this operation takes place once every four RS time periods or, after the track 4 read head has traversed one digit segment of each of the registers therein.

At each resetting of the vertical staircase generator D/U-4.7, a negative-going voltage transition is provided at the output of the vertical staircase generator and transmitted to the input of the horizontal staircase generator, thereby stepping the horizontal staircase generator D/U-4.8.

The horizontal staircase generator is reset once every revolution of the drum. The reset signal is obtained on the H bus 9:1R2 when this bus has a negative transition thereon. This negative transition is delayed and inverted in the one shot D/U-4.1 to provide a positive-going transition on the reset horizontal bus 9:1R3. This positive-going transition is applied to the reset horizontal bus 10:1L3, this bus being an input terminal of the horizontal staircase generator, and resets this circuit to its initial condition. The output of the vertical staircase generator is applied over the vertical staircase buses 10:1R1 and 11:1L11 to one of the input terminals of the vertical amplifier D/U-6.1.

The output of the horizontal staircase generator is applied along the horizontal staircase buses 10:1R2 and 11:1L12 to one of the input terminals of the horizontal amplifier D/U-6.2.

The output waveforms of the vertical and horizontal staircase generators are indicated on FIGURES 62.

Additional signals required to develop the relative positions of the strokes for each character are produced in the following manner:

The track 6 timing signals, previously discussed, are applied along the shift bus 9:1R1 to the shift bus 10:1L4. For each of the 7 pulses obtained from track 6 as discussed supra, a positive-going voltage transition will be obtained, this positive voltage transition being applied to the complement input of the segment generator flip flop No. 1 D/U-4.9 (FIGURE 16), alternately setting and resetting this flip flop. Initially, all of the flip flops D/U-4.9 to D/U-4.12 of the segment generator are in the set condition, i.e., each of the FF outputs thereof are at a negative voltage level.

After the seven strokes have been obtained from the track 6 read head, the next succeeding signal on the RS bus 9:1R6 will provide a positive-going transition on the reset segment generator bus 9:1R5 and 10:1L5 to 50 reset the segment flip flops D/U-4.9, D/U-4.10, D/U-4.11 and D/U-4.12 of FIGURE 16. As mentioned hereinabove, a resetting of the segment generator places all of the segment generator flip flops in the set condition.

The segment flip flops D/U-4.9, D/U-4.10 and D/U-4.11 of the segment or stroke generator act as an up counter because the setting of the segment No. 1 flip flop will cause the segment No. 2 flip flop to be reset while the setting of the segment No. 2 flip flop will cause the segment No. 4 flip flop to be reset, thus producing a binary output signal pattern as indicated in FIGURE 61. The No. 4' flip flop of the segment generator D/U-4.12 produces a signal output with a staggered timing pattern in relation to the No. 4 flip flop D/U-4.11. The output signal from the No. 4' flip flop D/U-4.12 will shift the output of a sine wave producing stroke oscillator D/U-5.3 between the vertical and horizontal deflection amplifiers as required.

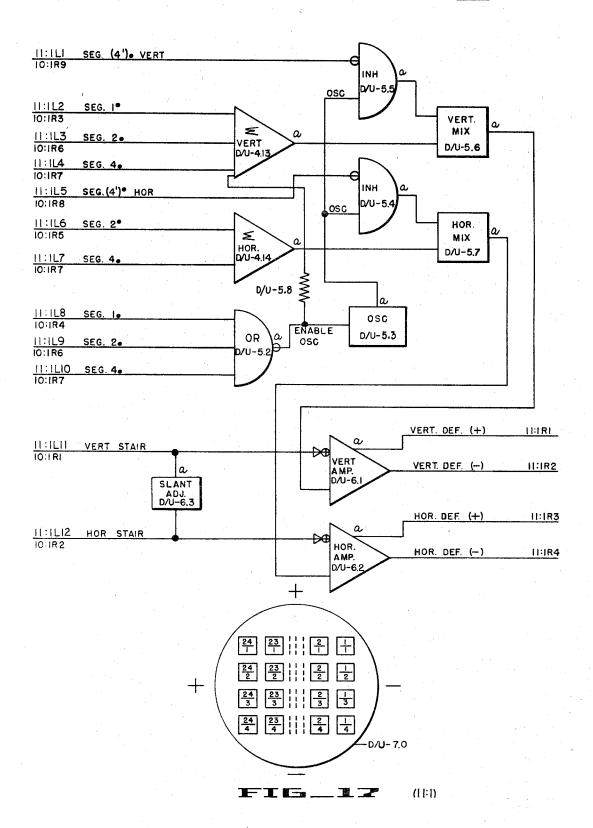

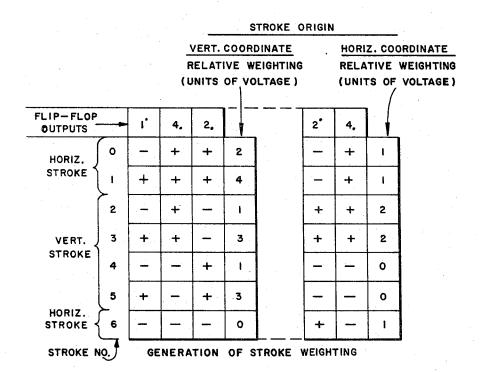

The segment generator outputs labelled SEG 1 70 (10:1R3), SEG 2 (10:1R6) and SEG 4 (10:1R7) are applied to the input terminals of the vertical summing network D/U-4.13 (FIGURE 17). The vertical summing network produces an output voltage based upon the condition of the three inputs thereto from the seg-75

ment generator. The vertical summing circuit therefore provides an output voltage which is weighted in accordance with the condition of the inputs thereto. The specific weighting of the output voltage of the vertical summing circuit as based on input conditions is set forth in FIG-URE 65.

An additional input is applied to the vertical summing network through a resistor D/U-5.8 which originates at the output of the oscillator OR gate D/U-5.2 which resistor is part of a circuit (not shown) for providing a decimal point,

The output of the vertical summing network is applied to an input terminal of the vertical mixing network D/U-5.6 which, when not inhibited by the inhibit gate D/U-5.5, passes vertical deflection signals to the vertical deflection amplifier D/U-6.1.

The inhibit gate D/U-5.5 passes signals therethrough from the oscillator D/U-5.3 to the vertical mixing network to provide the required oscillatory scan for making a line trace. The inhibit gate D/U-5.5 is enabled when a negative voltage level appears on the input 11:1L1. The situation occurs when the No. 4' flip flop of the segment generator is in the set condition, i.e., the SEG (4') output is at a negative voltage level.

The segment generator outputs labelled SEG 2 (10:1R5) and SEG 4 (10:1R7) are applied to the input terminals of the horizontal summing network D/U-4.14 (FIGURE 17). The horizontal summing network produces an output voltage based upon the condition of the inputs thereto from the segment generator. The horizontal summing circuit therefore provides an output voltage which is weighted in accordance with the condition of the inputs thereto. The specific weighting of the output voltage of the horizontal summing circuit as based on input conditions is set forth in FIGURE 65.

The output of the horizontal summing network is applied to an input terminal of the horizontal mixing network D/U-5.7 which, when not inhibited by the inhibit gate D/U-5.4, passes horizontal deflection signals to the horizontal deflection amplifier D/U-6.2.

The inhibit gate D/U-5.4 is identical to inhibit gate D/U-5.5, described hereinabove. This gate operates when gate D/U-5.5 is not operating because, whereas the gate D/U-5.5 is coupled to the FF output of the No. 4' flip flop of the segment generator, the gate D/U-5.4 is coupled to the FF output of this same flip flop.

The two inhibit gates D/U-5.5 and D/U-5.4 control the path taken by the oscillator stroke-producing signal by the application of signals from the segment generator. That is, the output of the pigment flip flop No. 4' FF terminal 10:1R9 is applied to the inhibit gate D/U-5.5, thereby enabling this gate and transferring the oscillator signal to the vertical deflection amplifiers.

The output of the segment flip flop No. 4' FF terminal 10:1R8 controls the inhibit gate D/U-5.4, this gate controlling the transfer of the oscillator stroke signal to the horizontal deflection amplifier when enabled by the signal of bus 10:1R8. The sequence of the stroke generation pattern is shown in FIGURES 64 and 65.

A slant adjustment circuit D/U-6.3 is coupled between the buses 11:1L11 and 11:1L12.

Typical generation of the character stroke proceeds as follows:

Initially, all of the flip flops D/U-4.9 to D/U-4.12 of the segment generator (FIGURE 16) are in the set condition. Therefore, initially, the segment generator provides a negative voltage level on the SEG 1 bus, a positive voltage level on the SEG 2 bus, a negative voltage level on the SEG 4 bus. Therefore, initially, the segment generator will provide an output voltage configuration as shown for stroke No. Zero (0) in FIGURE 65. The vertical coordinate will have a weight of two (2) and the horizontal coordinate will have a weight of one (1).

The weights are determined in the following manner.

55

18 SUMMARY OF THE "FLIP FLOP MODES OF

A positive voltage level on the SEG 1 output of the segment generator provides a weight of two (2). A positive voltage level on SEG 2, SEG 2, or SEG 4, outputs provides a weight of one (1). Negative voltage levels on these outputs provide a weight of zero (0).

When the first pulse from track 6 of the drum is applied through TK6 read head and associated circuitry (FIG-URE 15) to the shift input 10:1L4 of the segment generator, the generator counts one count and provides the configuration of outputs set forth for stroke No. 1 in 10 FIGURE 65. In this condition the output SEG 1. is at a positive voltage level as are the SEG 2, and SEG 4, outputs. The SEG 2 output is at a negative voltage level. In this manner a vertical weight of four (4) is provided and a horizontal weight of one (1) is provided, corresponding  $_{15}$ to stroke No. 1 in FIGURE 65.

The next pulse from track 6 shifts the segment generator to the stroke No. 2 condition as set forth in FIGURE 65 and all subsequent pulses from track 6 will provide generation of the remaining strokes in order, as shown in 20 FIGURES 64 and 65.

The FF output of the No. 4' segment flip flop will be at a negative voltage level during the zero stroke time and thus will enable the inhibit gate D/U-5.4, thereby causing a stroke signal as produced by the oscillator D/U-5.3 25 to be directed to the horizontal deflection amplifier D/U-6.2. Also, during the No. 1 and No. 6 stroke times. the inhibit gate D/U-5.4 will remain enabled, again producing a horizontal stroke during the No. 1 stroke time. During the No. 2, No. 3, No. 4 and No. 5 stroke times 30 the FF output of the No. 4' segment flip flop will be at a negative voltage level, thereby causing a stroke signal as produced by the oscillator to be directed to the vertical deflection amplifier D/U-6.1.

This operation is carried on for the remaining strokes 35 in a similar manner to generate each segment of the "8" pattern of FIGURE 64. As mentioned supra, the desired character is scanned on the face of the CRT by timely blanking the grid of the CRT when the unwanted strokes of the figure "8" are scanned, thereby eliminating certain 40 ones of the figure "8" strokes. This is provided since both the shift register (FIGURE 15) and the segment generator (FIGURE 16) are stepped by the same timing pulses from track 6 of the drum, thereby providing synchronism therebetween. In this manner, the contents of the track 4 45 registers are displayed on the face of the CRT.

FIGURES 42 to 60 set forth a typical circuit diagram of the preferred embodiment of the invention previously described.

Before discussing the circuit diagram, it will first be necessary to set forth the conventions utilized and the contents of various blocks depicting a typical circuit configuration.

# CONVENTIONS

In order that the buses of the various sheets of drawing be easily followed, bus numbers have been provided, some of which appear above the bus line and some of which appear below the bus line. The numbers include a 60 first number, a letter (T, B, L or R) and a second number. The first number refers to the sheet number in parentheses () rather than the figure number. The letter indicated top (T), bottom (B), left (L) and right (R). The second number indicates the number of the bus.

All bus numbers appearing above a bus line refer to that bus on that sheet. All bus numbers appearing below a bus line refer to the sheet or sheets and bus thereon to which this bus is connected. For example, a number **167T2** above a bus line indicates a bus which leaves sheet (167) at the top thereof and is the second top bus going from left to right. A number 173L1 below a bus line indicates that the bus line continues at sheet (173), the

OPERATION" DIAGRAM (FIGURE 18) Referring to FIGURE 18, the table therein defines the RESET ("0") and the SET ("1") conditions for the several flip flops numbered I, II, III used in the circuit. The flip flops are defined as being RESET if output b thereof

is at a negative voltage level and output a thereof is at a positive voltage level. The values provided in this table

are approximate values only.

FIGURE 18 also illustrates all possible input and output configurations, though it is apparent, by referring to the individual flip flop diagrams, that only certain combinations of these inputs are used with any given flip flop. This diagram will serve primarily as a reference aid to location of flip flop terminals. As set forth in FIGURE 18, the following inputs require a positive transition signal (i.e., a rapid change in voltage levels from a negative voltage to a positive voltage level), i, h, g, f. The following inputs operate by the application of a positive pulse: d (T), c (W), a, b. (Note: connections a and b may be considered as bifunctional connections in the sense that these connections primarily function as outputs. However, a positive pulse may be introduced into the flip flop to momentarily force the appropriate output connection to a positive voltage level.) Terminals j and e serve as static inputs, i.e., changes of voltage levels at these inputs do not, of themselves, change the state of the flip flop. Rather, these "gate" inputs serve to retain appropriate voltage levels until it is desired to transfer these levels to the corresponding output terminals a and b by the application of a positive transition signal to the input c (W). Input d (T) operates as a "toggle" input. That is, the flip flop will continue to change states upon the application of successive positive transition signals thereto. As shown in FIGURE 45, a positivegoing transition on the f and h input terminals will set the flip flop, whereas a positive-going transition on the g and i input terminals will reset the flip flop. If the g and h input terminals are tied together, these inputs will then operate as a complementing input for all positive-going transitions applied thereto, thereby alternately setting and resetting this flip flop. A positive voltage level applied to the b input terminal will set the flip flop, whereas a positive voltage level applied to the a input terminal will reset the flip flop.

The above symbology will be utilized in depicting all flip flops in FIGURES 42 to 60.

FIGURE 19 illustrates the operation of a typical one shot circuit. Upon the application of a positive transition signal at the left-hand input (denoted by a diamond shaped symbol), the one shot circuit will produce a negative output signal. The pulse width of this signal is determined by the RC time constant of the one shot. The letter M signifies a connection point to the one shot circuit wherein an external capacitor may be connected from point M to the output connection in order to change the pulse width of the output signal.

## FLIP FLOP 1

# Circuit operation

FIGURES 20 and 21 set forth the circuit diagram and block diagram of the type I flip flop. The type I flip flop is typical of the type circuit designed to remain in one of two stable states at the termination of a triggering signal thereto. Six separate input terminals are available, two of which make use of bifunctional connections being primarily operated as outputs. The four connections used as inputs only are labelled: i, h, g, and f. Two outputs (previously mentioned as bifunctional connections) are provided: a and b. A typical cycle of operation follows wherein it is assumed that the flip flop is reset, i.e., in FIGURE 20, Q2 is "on" (conducting) and Q1 is "off" (non-conducting). Assuming further that a positive transition signal is to be applied to the h input, the h input would be initially at a first bus down from the top on the left side of sheet (173). 75 negative level. The lower side of capacitor C3 would then be at a negative voltage level. Also, the upper side of this capacitor would be at a positive voltage level because of the connection thereat to the collector of transistor Q2 through resistor RS5. As a result, capacitor C3 will have a charge of approximately 6 volts thereacross. At the arrival of the positive-going transition pulse, the lower side of the capacitor C3 will be driven to a positive voltage level, causing the upper side of capacitor C3 to be driven to a level of approximately +6 volts. The diode D4, pointing toward and connected to the base of transistor Q2, 10 will transfer this positive transition signal to the base of transistor Q2, causing this transistor to be turned "off."